Electrical Specifications

68 Datasheet

Notes:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies.

2. The voltage rail V

CCD

which will be set to 1.50V or 1.35V nominal depending on the voltage of all DIMMs connected to the

processor.

3. V

IL

is the maximum voltage level at a receiving agent that will be interpreted as a logical low value.

4. V

IH

is the minimum voltage level at a receiving agent that will be interpreted as a logical high value.

5. V

IH

and V

OH

may experience excursions above V

CCD

. However, input signal drivers must comply with the signal quality

specifications.

6. This is the pull down driver resistance. Reset drive does not have a termination.

7. R

VTT_TERM

is the termination on the DIMM and not controlled by the processor. Refer to the applicable DIMM datasheet.

8. The minimum and maximum values for these signals are programmable by BIOS to one of the pairs.

9. COMP resistance must be provided on the system board with 1% resistors. DDR01_RCOMP[2:0] and DDR23_RCOMP[2:0]

resistors are terminated to V

SS

.

10. Input leakage current is specified for all DDR3 signals.

11. DRAM_PWR_OK_C{01/23} must have a maximum of 30 ns rise or fall time over VCCD * 0.55 +300mV and -200mV and the

edge must be monotonic.

12. The DDR01/23_RCOMP error tolerance is ±15% from the compensated value.

13. DRAM_PWR_OK_C{01/23}: Data Scrambling must be enabled for production environments. Disabling Data scrambling can be

used for debug and testing purposes only. Running systems with Data Scrambling off will make the configuration out of

specification. For details, refer to the processor Datasheet, Volume 2 of 2; see Related Documents section.

Notes:

1. V

TTD

supplies the PECI interface. PECI behavior does not affect V

TTD

minimum/maximum specification

2. It is expected that the PECI driver will take into account the variance in the receiver input thresholds and be able to drive its

output within safe limits (-0.150V to 0.275*V

TTD

for the low level and 0.725*V

TTD

to V

TTD

+0.150V for the high level).

3. The leakage specification applies to powered devices on the PECI bus.

4. One node is counted for each client and one node for the system host. Extended trace lengths might appear as additional

nodes.

5. Excessive capacitive loading on the PECI line may slow down the signal rise/fall times and consequently limit the maximum bit

rate at which the interface can operate.

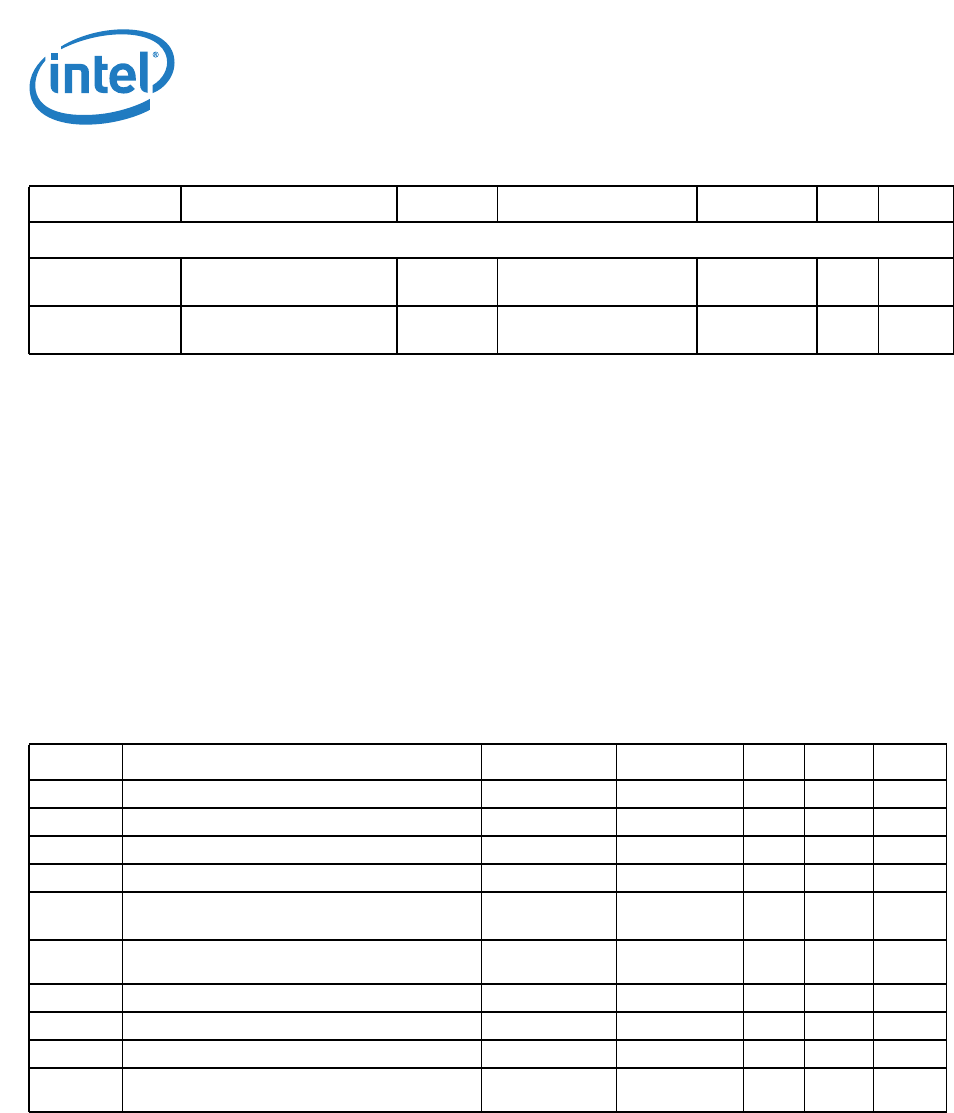

DDR3 Miscellaneous Signals

V

IL

Input Low Voltage

DRAM_PWR_OK_C{01/23}

——

0.55*V

CCD

+

0.2

V

2, 3,

11, 13

V

IH

Input High Voltage

DRAM_PWR_OK_C{01/23}

0.55*V

CCD

+ 0.3

——V

2, 4, 5,

11, 13

Table 7-14. PECI DC Specifications

Symbol Definition and Conditions Min Max Units Figure Notes

1

V

In

Input Voltage Range -0.150 V

TT

V— —

V

Hysteresis

Hysteresis 0.100 * V

TT

—V——

V

N

Negative-edge threshold voltage 0.275 * V

TT

0.500 * V

TT

V 7-1 2

V

P

Positive-edge threshold voltage 0.550 * V

TT

0.725 * V

TT

V 7-1 2

I

SOURCE

High level output source

V

OH

= 0.75 * V

TT

-6.0 — mA — —

I

Leak+

High impedance state leakage to V

TTD

(V

leak

=

V

OL

)

50 200 μA— 3

R

ON

Buffer On Resistance 20 36 —

C

Bus

Bus capacitance per node N/A 10 pF — 4, 5

V

Noise

Signal noise immunity above 300 MHz 0.100 * V

TT

N/A V

p-p

——

Output Edge Rate (50 ohm to VSS, between V

IL

and V

IH

)

1.5 4 V/ns — —

Table 7-13. DDR3 and DDR3L Signal DC Specifications (Sheet 2 of 2)

Symbol Parameter Min Typ Max Units Notes

1