Datasheet 45

Signal Descriptions

PE2B_TX_DN[7:4]

PE2B_TX_DP[7:4]

PCIe Transmit Data Output

PE2C_TX_DN[11:8]

PE2C_TX_DP[11:8]

PCIe Transmit Data Output

PE2D_TX_DN[15:12]

PE2D_TX_DP[15:12]

PCIe Transmit Data Output

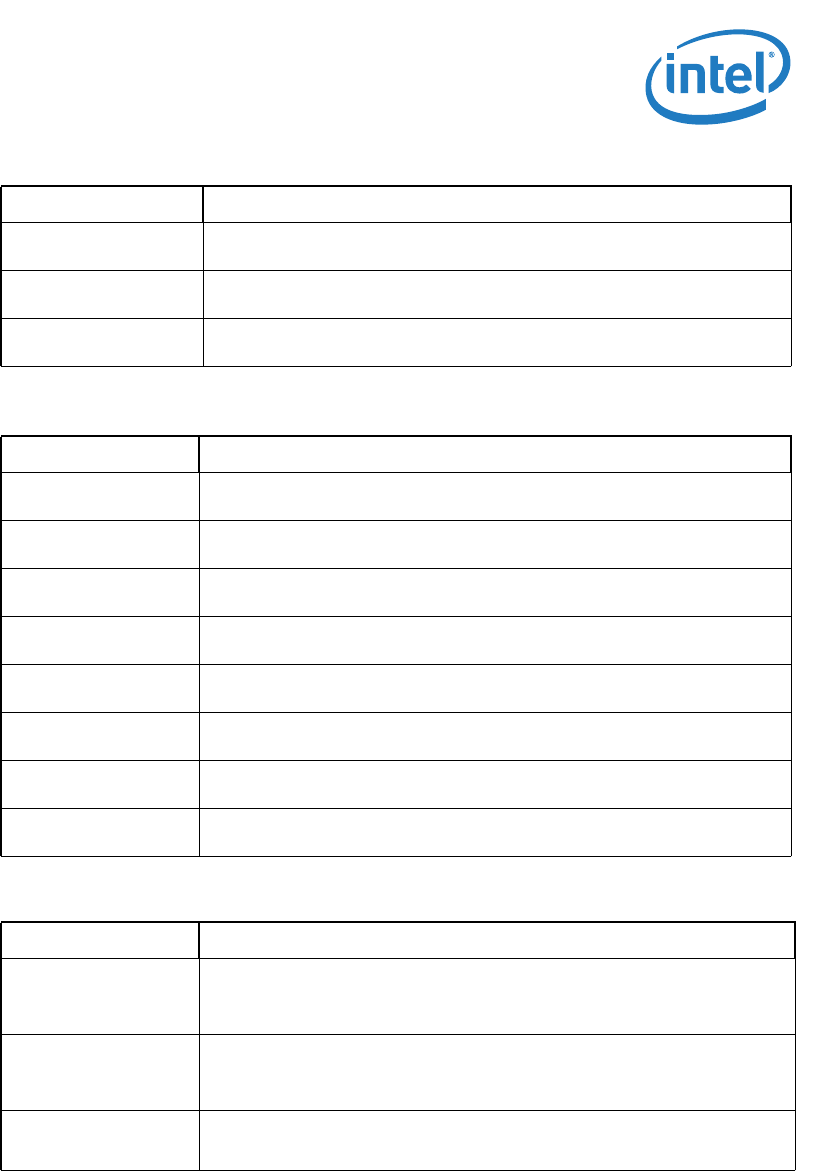

Table 6-5. PCI Express* Port 3 Signals

Signal Name Description

PE3A_RX_DN[3:0]

PE3A_RX_DP[3:0]

PCIe Receive Data Input

PE3B_RX_DN[7:4]

PE3B_RX_DP[7:4]

PCIe Receive Data Input

PE3C_RX_DN[11:8]

PE3C_RX_DP[11:8]

PCIe Receive Data Input

PE3D_RX_DN[15:12]

PE3D_RX_DP[15:12]

PCIe Receive Data Input

PE3A_TX_DN[3:0]

PE3A_TX_DP[3:0]

PCIe Transmit Data Output

PE3B_TX_DN[7:4]

PE3B_TX_DP[7:4]

PCIe Transmit Data Output

PE3C_TX_DN[11:8]

PE3C_TX_DP[11:8]

PCIe Transmit Data Output

PE3D_TX_DN[15:12]

PE3D_TX_DP[15:12]

PCIe Transmit Data Output

Table 6-6. PCI Express* Miscellaneous Signals

Signal Name Description

PE_RBIAS

PCI RBIAS: This input is used to control PCI Express* bias currents. A 50 ohm

1% tolerance resistor must be connected from this land to V

SS

by the platform.

PE_RBIAS is required to be connected as if the link is being used even when PCIe*

is not used.

PE_RBIAS_SENSE

PCI RBIAS Sense: This signal provides dedicated bias resistor sensing to

minimize the voltage drop caused by packaging and platform effects.

PE_RBIAS_SENSE is required to be connected as if the link is being used even

when PCIe* is not used.

PE_VREF_CAP

PCI Express* Voltage Reference: PE_VREF_CAP is used to measure the actual

output voltage and comparing it to the assumed voltage. A 0.01 uF capacitor must

be connected from this land to V

SS

.

Table 6-4. PCI Express* Port 2 Signals (Sheet 2 of 2)

Signal Name Description