Datasheet 49

Signal Descriptions

TXT_AGENT

Intel

®

Trusted Execution Technology (Intel

®

TXT) Agent: This is a strap

signal:

0 = Default. The socket is not the Intel

®

TXT Agent.

1 = The socket is the Intel

®

TXT Agent.

In non-Scalable dual-processor (DP) platforms, the legacy socket (identified by

SOCKET_ID[1:0] = 00b) with Intel TXT Agent should always set the TXT_AGENT

to 1b.

On Scalable DP platforms the TXT AGENT is at the Node Controller.

This signal is pulled down on the die (refer to Table 7-6 for details).

TXT_PLTEN

Intel

®

Trusted Execution Technology (Intel

®

TXT) Platform Enable: This is

a strap signal:

0 = The platform is not Intel

®

TXT enabled. All sockets should be set to zero.

Scalable DP (sDP) platforms should choose this setting if the Node Controller

does not support Intel TXT.

1 = Default. The platform is Intel TXT enabled. All sockets should be set to one.

In a non-Scalable DP platform this is the default. When this is set, Intel TXT

functionality requires the user to explicitly enable Intel TXT using BIOS

setup.

This signal is pulled up on the die (refer to Table 7-6 for details).

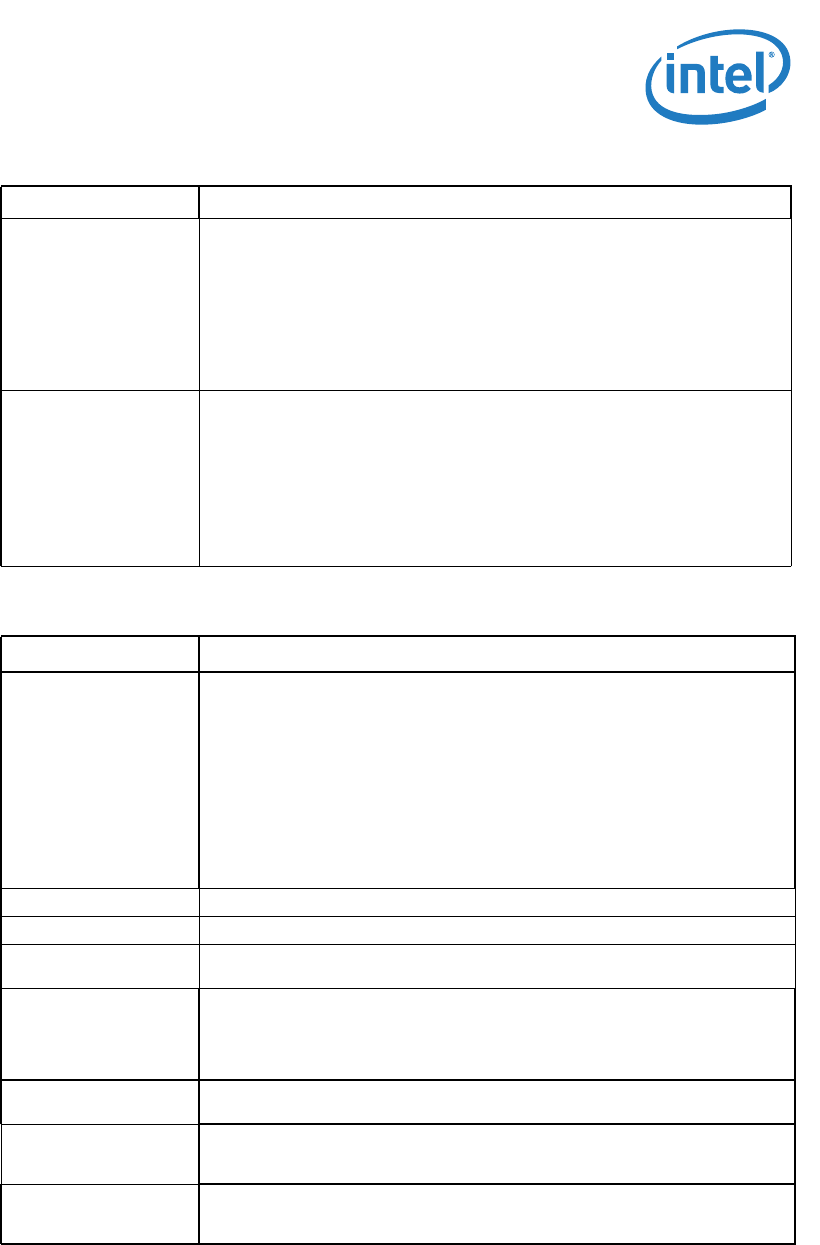

Table 6-13. Miscellaneous Signals

Signal Name Description

BCLK_SELECT[1:0]

BCLK Select: These configuration straps are used to inform the processor that a

non-standard value for BCLK will be applied at reset. A "11" encoding on these

inputs informs the processor to run at DEFAULT BCLK = 100 MHz. These signals

have internal pull-up to V

TT

.

The encoding is as follows:

BCLK_SELECT1 BCLK_SELECT0 BCLK Selected

X X 100 MHz (default)

1 1 100 MHz

1 0 125 MHz

0 1 Reserved

0 0 Reserved

CORE_VREF_CAP A capacitor must be connected from this land.

CORE_RBIAS This input is used to control bias currents.

CORE_RBIAS_SENSE

This signal provides dedicated bias resistor sensing to minimize the voltage drop

caused by packaging and platform effects.

PROC_SEL_N

Processor Selected: This output can be used by the platform to determine if the

installed processor is an Intel

®

Core™ i7 processor family for LGA2011 socket or a

future processor. There is no connection to the processor silicon for this signal.

This signal is also used by the V

CCPLL

and V

TT

rails to switch their output voltage to

support future processors.

RSVD

RESERVED: All signals that are RSVD must be left unconnected on the board.

Refer to Section 7.1.9 for details.

SKTOCC_N

Socket Occupied: SKTOCC_N is used to indicate that a processor is present. This

is pulled to ground on the processor package; there is no connection to the

processor silicon for this signal.

TESTHI_BH48

TESTHI_BF48

TESTHI_AT50

Test High: TESTHI_XX signal must be pulled up on the board.

Table 6-12. Processor Asynchronous Sideband Signals (Sheet 3 of 3)

Signal Name Description