DS33Z41 Quad IMUX Ethernet Mapper

109 of 167

Register Name:

LI.RHPMUU

Register Description:

Serial Interface Receive HDLC PMU Update Register

Register Address:

120h

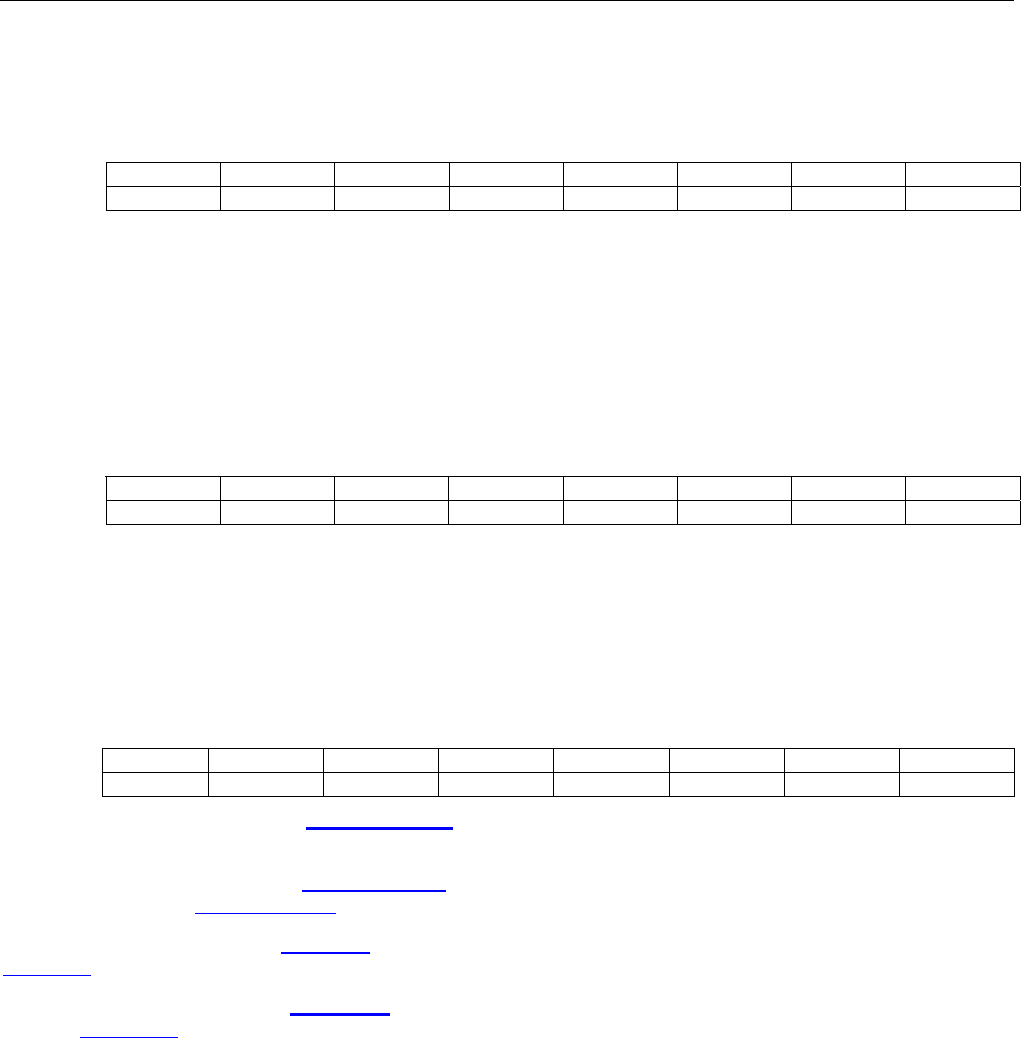

Bit # 7 6 5 4 3 2 1 0

Name — — — — — — — RPMUU

Default 0 0 0 0 0 0 0 0

Bit 0: Receive PMU Update (RPMUU). This signal causes the receive cell/packet processor block performance

monitoring registers to be updated. A 0 to 1 transition causes the performance monitoring registers to be updated

with the latest data, and resets the associated counters. This bit updates performance monitoring counters for the

Serial Interface.

Register Name:

LI.RHPMUS

Register Description:

Serial Interface Receive HDLC PMU Update Status Register

Register Address:

121h

Bit # 7 6 5 4 3 2 1 0

Name — — — — — — — RPMUUS

Default 0 0 0 0 0 0 0 0

Bit 0: Receive PMU Update Status (RPMUUS). This bit is set when the Transmit PMU Update is completed.

This bit is cleared when RPMUU is set to 0.

Register Name:

LI.RX86S

Register Description:

Receive X.86 Latched Status Register

Register Address:

122h

Bit # 7 6 5 4 3 2 1 0

Name — — — — SAPIHNE SAPILNE CNE ANE

Default — — — — — — — —

Bit 3: SAPI High is Not Equal to LI.TRX86SAPIH Latched Status (SAPIHNE). This latched status bit is set if

SAPIH is not equal to LI.TRX86SAPIH. This latched status bit is cleared upon read.

Bit 2: SAPI Low is Not Equal to LI.TRX86SAPIL

Latched Status (SAPILNE). This latched status bit is set if

SAPIL is not equal to LI.TRX86SAPIL

. This latched status bit is cleared upon read.

Bit 1: Control is Not Equal to LI.TRX8C

(CNE). This latched status bit is set if the control field is not equal to

LI.TRX8C

. This latched status bit is cleared upon read.

Bit 0: Address is Not Equal to LI.TRX86A

(ANE). This latched status bit is set if the X.86 Address field is not

equal to LI.TRX86A. This latched status bit is cleared upon read.