DS33Z41 Quad IMUX Ethernet Mapper

59 of 167

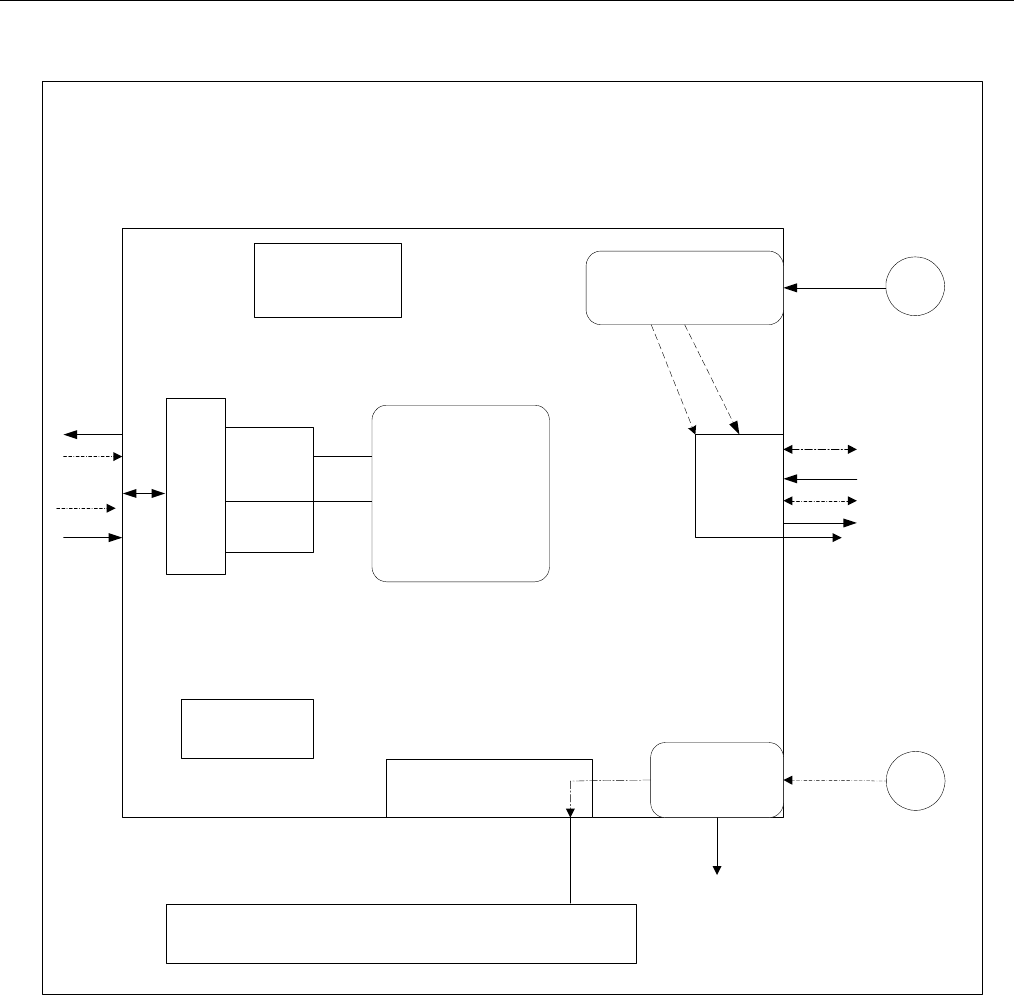

Figure 8-16. CIR in the WAN Transmit Path

MAC

RMII

MII

SDRAM

Interface

Buffer Dev

Div by 2,4,12

Output Clocks

25,50

Mhz

100 Mhz Oscillator

SYSCLKI

SDCLKO

Buffer

Dev

Div by 1,2,4,8,10

Output clocks:

50,25 Mhz,2.5 Mhz

50 or 25 Mhz Oscillator

TX_CLK1

RX_CLK1

TCLKI1

RCLKI1

REF_CLKO

50 or 25 Mhz

MDC

REF_CLKI

SDRAM

HDLC

+

Serial

Interface

CIR

Line 1

Arbiter

X.86

TSER

RSER

RXD

TXD

Microport

JTAG

IMUX