DS33Z41 Quad IMUX Ethernet Mapper

141 of 167

Receive Data (RXD[3:0]) is clocked from the external PHY synchronously with RX_CLK. The RX_CLK signal is

2.5MHz for 10Mbps operation and 25MHz for 100Mbps operation. RX_DV is asserted by the PHY from the first

Nibble of the preamble in 100Mbps operation or first nibble of SFD for 10Mbps operation. The data on RXD[3:0] is

not accepted by the MAC if RX_DV is low or RX_ERR is high (in DTE mode). RX_ERR should be tied low when

in DCE Mode.

Figure 10-3. MII Receive Functional Timing

RXD[3:0]

RX_CLK

P R E A E M B L E

F C S

In RMII Mode, TX_EN is high with the first bit of the preamble. The TXD[1:0] is synchronous with the 50MHz

REF_CLK. For 10Mbps operation, the data bit outputs are updated every 10 clocks.

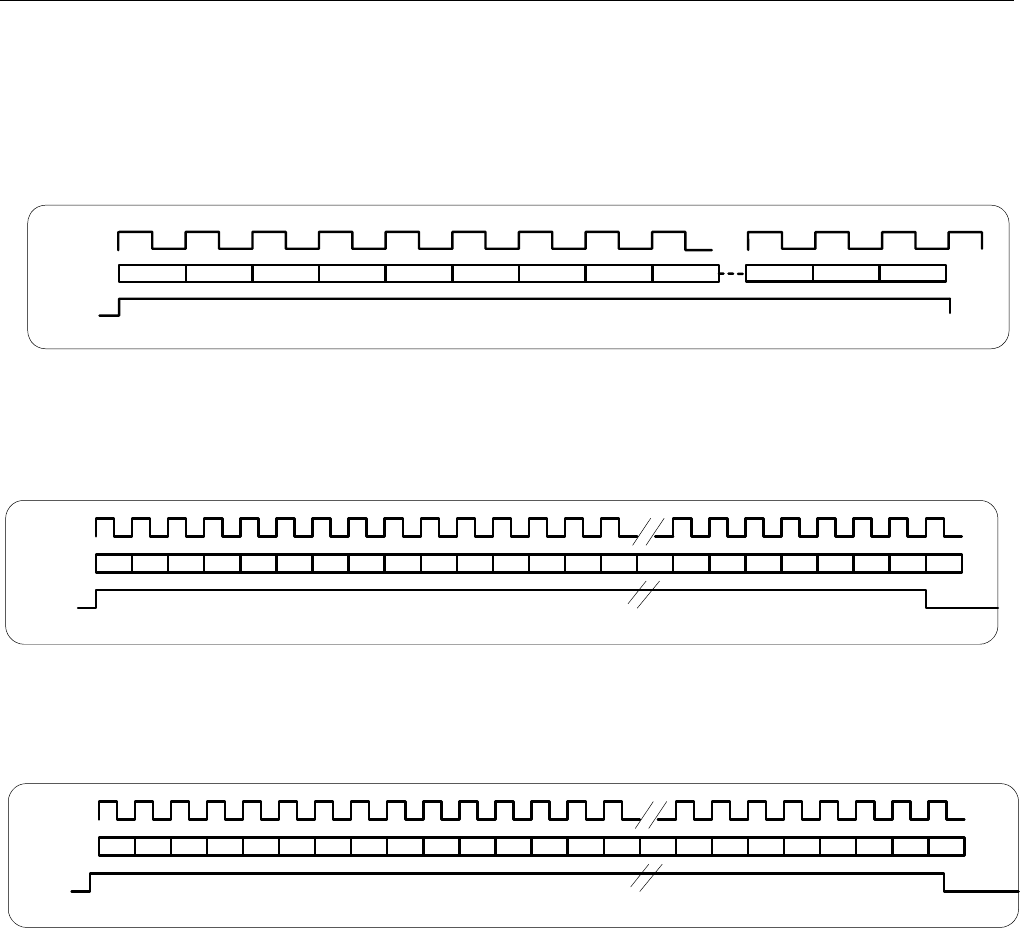

Figure 10-4. RMII Transmit Interface Functional Timing

TXD[1:0]

TX_EN

REFCLK

P R E A M B L E F C S

RMII Receive data on RXD[1:0] is expected to be synchronous with the rising edge of the 50MHz REF_CLK. The

data is only valid if CRS_DV is high. The external PHY asynchronously drives CRS_DV low during carrier loss.

Figure 10-5 RMII Receive Interface Functional Timing

RXD[1:0]

CRS_DV

REFCLK

P R E A M B L E F C S