DS33Z41 Quad IMUX Ethernet Mapper

115 of 167

Register Name:

SU.MACAWH

Register Description:

MAC Address Write High

Register Address:

14Bh

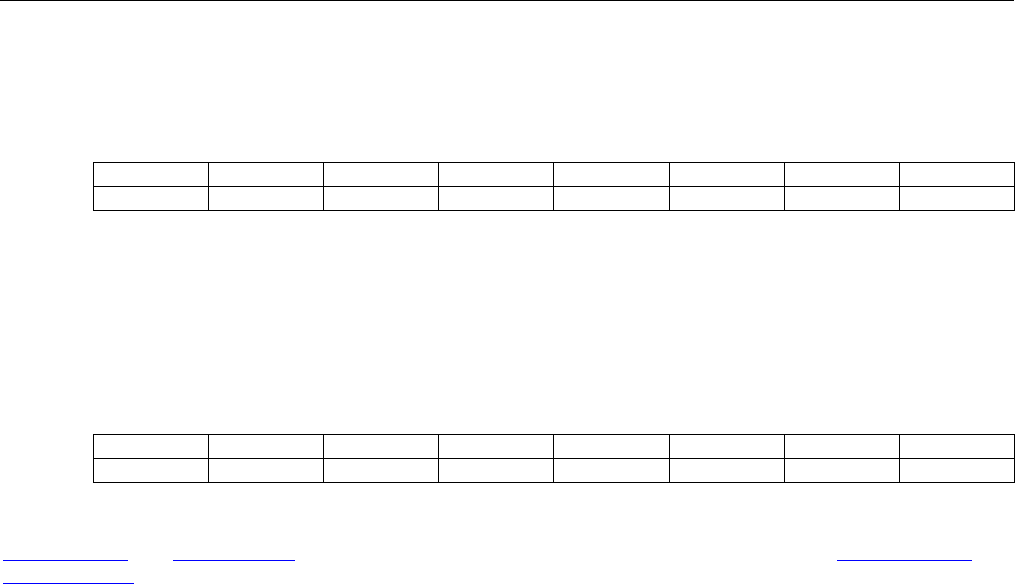

Bit # 7 6 5 4 3 2 1 0

Name MACAW 15 MACAW 14 MACAW 13 MACAW12 MACAW11 MACAW10 MACAW9 MACAW8

Default 0 0 0 0 0 0 0 0

Bits 7 to 0: MAC Write Address (MACAW15 to MACAW8). High byte of the MAC address. Used only for write

operations.

Register Name:

SU.MACRWC

Register Description:

MAC Read Write Command Status

Register Address:

14Ch

Bit # 7 6 5 4 3 2 1 0

Name — — — — — — MCRW MCS

Default 0 0 0 0 0 0 0 0

Bit 1: MAC Command RW (MCRW). If this bit is written to 1, a read is performed from the MAC. If this bit is

written to 0, a write operation is performed. Address information for write operations must be located in

SU.MACAWH

and SU.MACAWL. Address information for read operations must be located in SU.MACRADH and

SU.MACRADL

. The user must also write a 1 to the MCS bit, and the DS33Z41 will clear MCS when the operation

is complete.

Bit 0: MAC Command Status (MCS). Setting MCS in conjunction with MCRW will initiate a read or write to the

MAC registers. Upon completion of the read or write this bit is cleared. Once a read or write command has been

initiated the host must poll this bit to see when the operation is complete.