Chapter 2 Connecting Signals

SCXI-1141/1142/1143 User Manual 2-10 ni.com

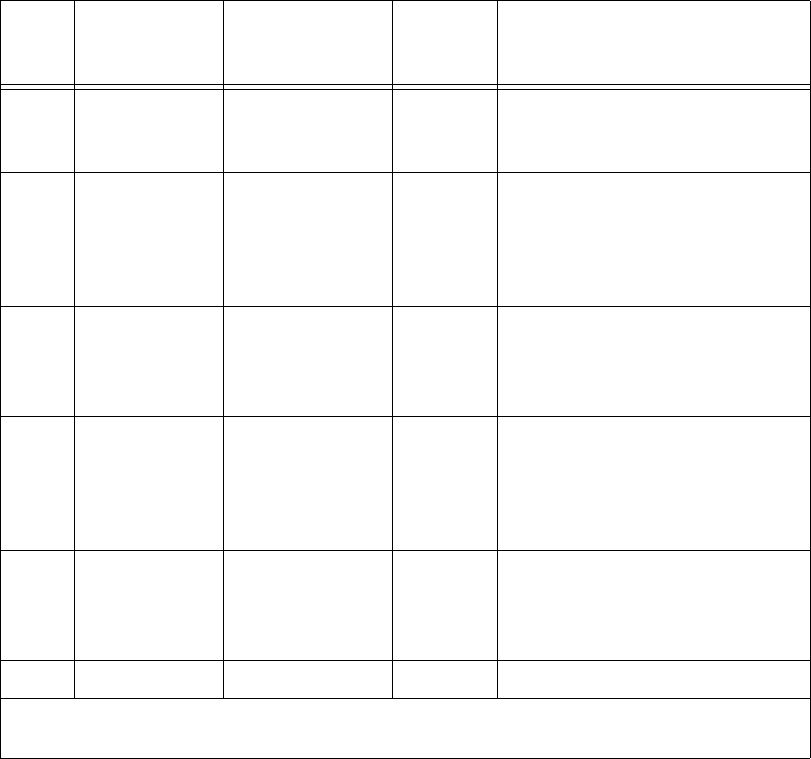

The signals on the rear signal connector are classified as analog output,

digital I/O, or timing I/O signals.

26 SER DAT OUT P0.4 Output Serial data out—this signal taps into

the SCXIbus MISO line to accept

serial output data from a module.

27 DAQ D*/A P0.1 Input Board data/address line—this signal

taps into the SCXIbus D*/A line to

indicate to the module whether the

incoming serial stream is data or

address information.

29 SLOT 0 SEL* P0.2 Input Slot 0 select—this signal taps into

the SCXIbus INTR* line to indicate

whether the information on MOSI is

being sent to a module or Slot 0.

36 SCAN CLK AI HOLD,

AI HOLD COMP

Input Scan clock—a rising edge indicates

to the scanned SCXI module that the

E/M Series DAQ device has taken a

sample and causes the module to

advance channels.

37 SER CLK EXT STROBE* Input Serial clock—this signal taps into

the SCXIbus SPI CLK line to clock

the data on the MOSI and MISO

lines.

43 RSVD RSVD Input Reserved.

Notes: All other pins are not connected.

An * means the signal is asserted low.

Table 2-3. SCXI-1141/1142/1143 Rear Communication Signals (Continued)

Pin

SCXI Signal

Name

NI-DAQmx

Device Signal

Name

Direction Description