HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 11 of 29

Detailed Timing Specifications

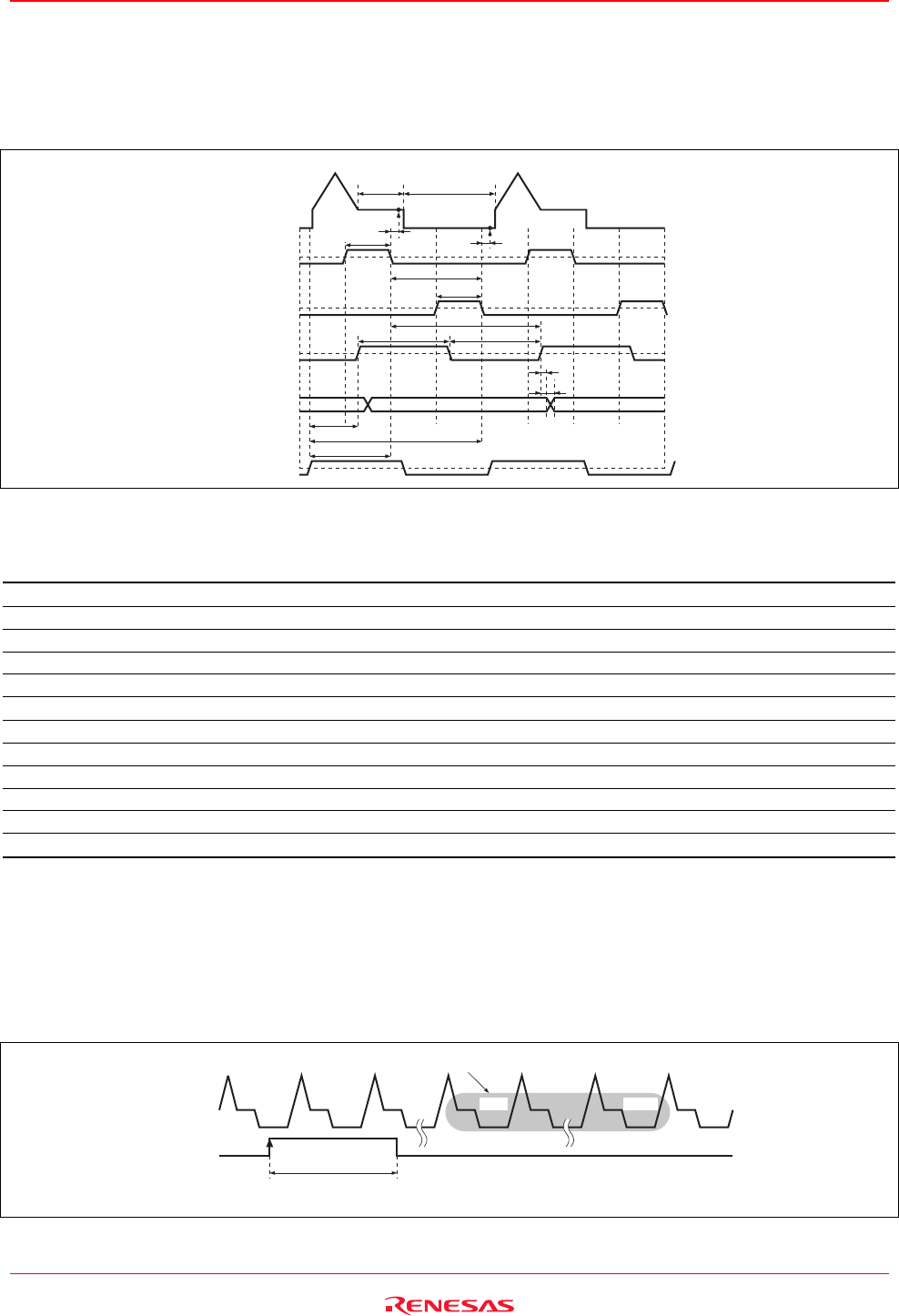

Detailed Timing Specifications when CDSIN Input Mode is Used

Figure 3 shows the detailed timing specifications when the CDSIN input mode is used, and table 8 shows each timing

specification.

CDS_in

SP1 Vth

(2)

(3)

SP2

A

DCLK

(7)

Vth

Vth

(8)

(9)

(10)

(4)

(1)

(5)

(11)

(6)

(13)

(12)

D0 to D9

H1

Black

level

Signal

level

Figure 3 Detailed Timing Chart when CDSIN Input Mode is Used

Table 8 Timing Specifications when the CDSIN Input Mode is Used

No. Timing Symbol Min Typ Max Unit

(1) Black-level signal fetch time t

CDS1

— (1.5) — ns

(2) SP1 ‘Hi’ period t

CDS2

Typ × 0.8 1/4f

CLK

Typ × 1.2 ns

(3) Signal-level fetch time t

CDS3

— (1.5) — ns

(4) SP2 ‘Hi’ period t

CDS4

Typ × 0.8 1/4f

CLK

Typ × 1.2 ns

(5) SP1 falling to SP2 falling time t

CDS5

Typ × 0.85 1/2f

CLK

Typ × 1.15 ns

(6) SP1 falling to ADCLK rising inhibit time t

CDS6

— (5) — ns

(7), (8) ADCLK t

WH

min./t

WL

min t

CDS7, 8

11 — — ns

(9) ADCLK rising to digital output holding time t

CHLD9

— (7) — ns

(10) ADCLK rising to digital output delay time t

COD10

— (16) — ns

(11) H1 rising to ADCLK rising time t

CDS11

— (1/4f

CLK

) — ns

(12) H1 rising to SPSIG falling time t

CDS12

— (1/f

CLK

) — ns

(13) H1 rising to SPBLK falling time t

CDS13

— (1/2f

CLK

) — ns

OBP Detailed Timing Specifications

Figure 4 shows the OBP detailed timing specifications.

The OB period is from the fifth to the twelfth clock cycle after the OB pulse is inputted. The average of the black

signal level is taken for eight input cycles during the OB period and it becomes the clamp level (DC standard).

CDS_in

OBP

N N+1 N+5 N+12 N+13

Note:

OB pulse > 2 clock cycles

OB period *

1

1. Shifts ±1 clock cycle depending on the OBP input timing.

Figure 4 OBP Detailed Timing Specifications