HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 15 of 29

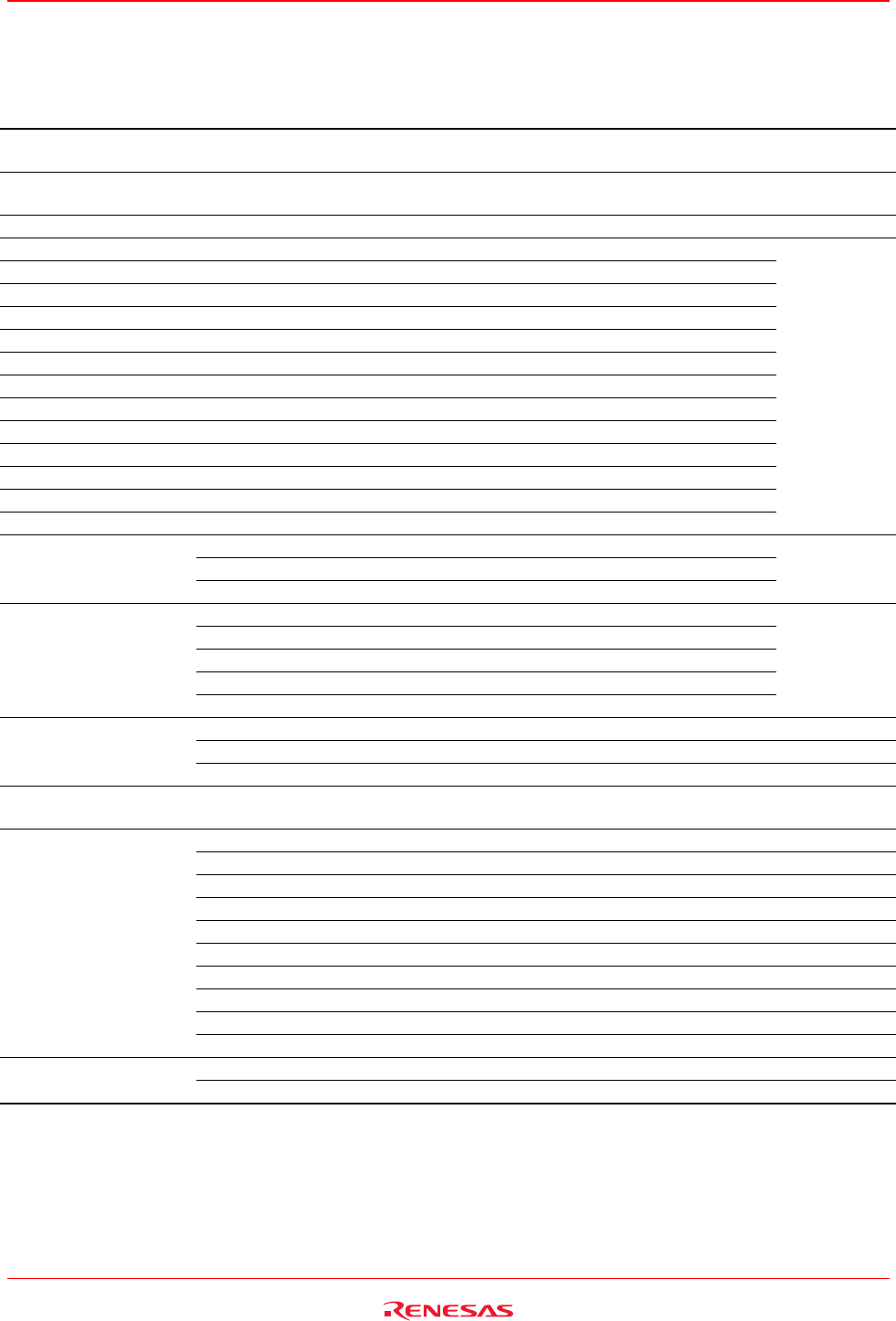

Electrical Characteristics (cont.)

(Unless othewide specified, Ta = 25°C, AV

DD

= 3.0 V, DV

DD

= 3.0 V, and R

BIAS

= 33 kΩ)

• Items for CDSIN Input Mode

Item Symbol Min Typ Max Unit Test Conditions Remarks

Consumption current (1) I

DD1

— 84 96.6 mA f

CLK

= 36 MHz

CDSIN mode

LoPwr = low

Consumption current (2) I

DD2

— 58 66.7 mA f

CLK

= 20 MHz

CDSIN mode

LoPwr = high

CCD offset tolerance range V

CCD

(–100) — (100) mV

Timing specifications (1) t

CDS1

— (1.5) — ns

Timing specifications (2) t

CDS2

Typ × 0.8 1/4f

CLK

Typ × 1.2 ns

Timing specifications (3) t

CDS3

— (1.5) — ns

Timing specifications (4) t

CDS4

Typ × 0.8 1/4f

CLK

Typ × 1.2 ns

Timing specifications (5) t

CDS5

Typ × 0.85 1/2f

CLK

Typ × 1.15 ns

Timing specifications (6) t

CDS6

1 5 9 ns

Timing specifications (7) t

CDS7

— 1/2f

CLK

— ns

Timing specifications (8) t

CDS8

— 1/2f

CLK

— ns

Timing specifications (9) t

CHLD9

— (7) — ns C

L

= 10 pF

Timing specifications (10) t

COD10

— (16) — ns C

L

= 10 pF

Timing specifications (11) t

CDS11

— (1/4f

CLK

) — ns

Timing specifications (12) t

CDS12

— (1/f

CLK

) — ns

Timing specifications (13) t

CDS13

— (1/2f

CLK

) — ns

Refer to table 8

CLP(00) — (14) — LSB

CLP(09) — (32) — LSB

Clamp level

CLP(31) — (76) — LSB

AGC(0) –4.4 –2.4 –0.4 dB

AGC(63) 4.1 6.1 8.1 dB

AGC(127) 12.5 14.5 16.5 dB

AGC(191) 21.0 23.0 25.0 dB

PGA gain at CDS input

AGC(255) 29.4 31.4 33.4 dB

*1

DLL_2 11 — 25 MHz *2

DLL_3 7 — 11 MHz *3

DLL operation frequency

DLL_4 5.5 — 7 MHz *4

T/G 3/1divided operation

frequency range

CLK_in3 28.6 — 28.6 MHz f

CLK

= 1/3CLK_in3

V

OH

2.94 2.97 — V 30 mA Buff, I

OH

= –5 mA

V

OL

— 22 47 MV 30 mA Buff, I

OL

= +5 mA

V

OH

2.89 2.94 — V 14 mA Buff, I

OH

= –5 mA

V

OL

— 50 112 MV 14 mA Buff, I

OL

= +5 mA

V

OH

2.91 2.96 — V 10 mA Buff, I

OH

= –3 mA

V

OL

— 36 78 MV 10 mA Buff, I

OL

= +3 mA

V

OH

2.85 2.93 — V 4 mA Buff, I

OH

= –2 mA

V

OL

— 60 129 MV 4 mA Buff, I

OL

= +2 mA

V

OH

2.69 2.86 — V 2 mA Buff, I

OH

= –2 mA

H Buffer output voltage

V

OL

— 115 262 mV 2 mA Buff, I

OL

= +2 mA

V

OH

2.81 2.90 — V I

OH

= –2 mA RG output voltage

V

OL

— 78 141 mV I

OL

= +2 mA

Notes: 1. Define digital output full scall with 1 V input as 0 dB.

2. Number of master steps: 60 steps, DLL current High

3. Number of master steps: 40 steps, DLL current Low

4. Number of master steps: 60 steps, DLL current Low

5. Values within parentheses ( ) are for reference.