HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 3 of 29

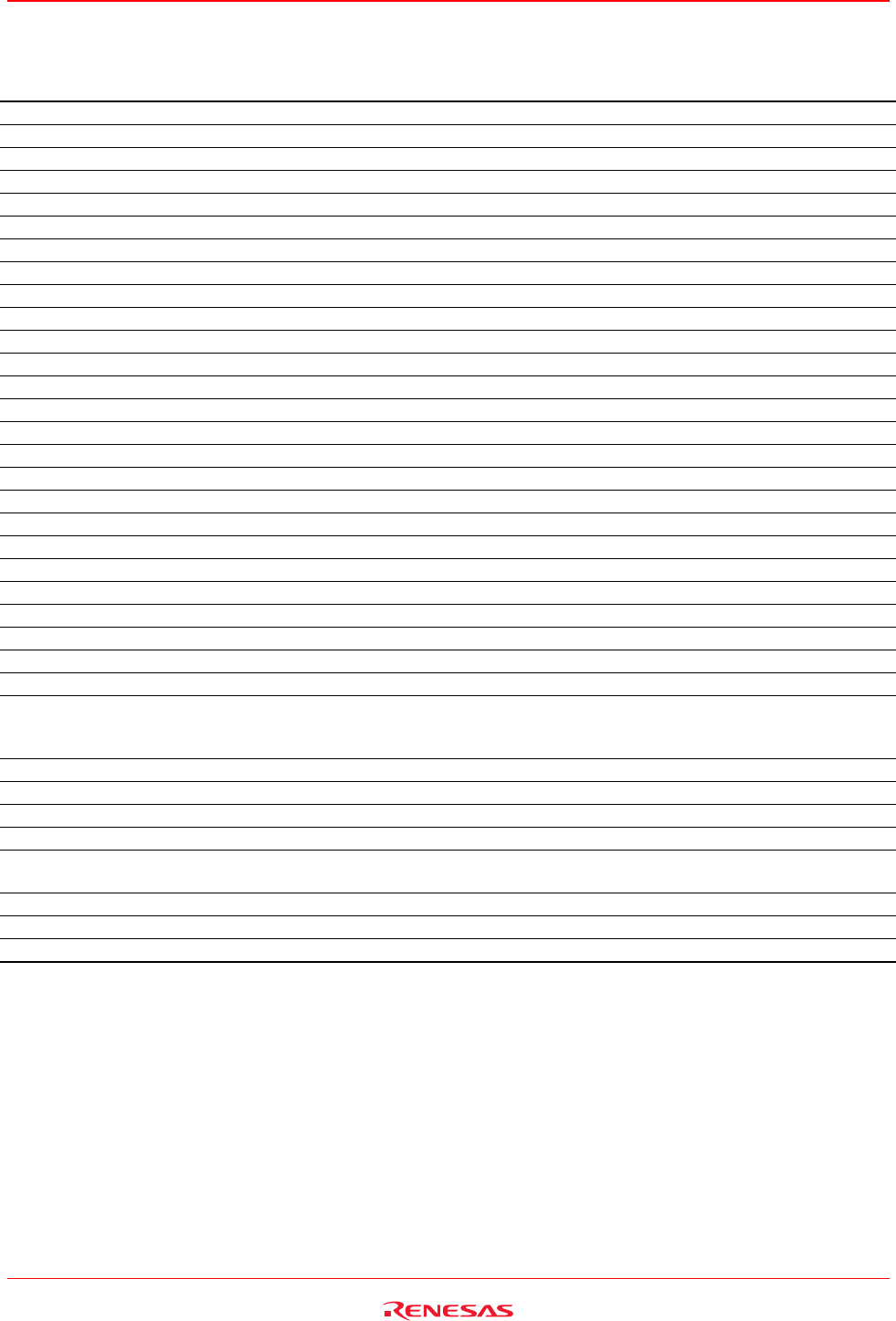

Pin Description (cont.)

Pin No.

Symbol

Description

I/O

Analog(A) or

Digital(D)

Remarks

30 XV1 V.CCD transfer pulse output-1 O D 2 mA/10 pF

31 XV2 V.CCD transfer pulse output-2 O D 2 mA/10 pF

32 XV3 V.CCD transfer pulse output-3 O D 2 mA/10 pF

33 XV4 V.CCD transfer pulse output-4 O D 2 mA/10 pF

34 CH1 Read out pulse output-1 O D 2 mA/10 pF

35 CH2 Read out pulse output-2 O D 2 mA/10 pF

36 CH3 Read out pulse output-3 O D 2 mA/10 pF

37 CH4 Read out pulse output-4/XV6 at stripe mode O D 2 mA/10 pF

38 XSUB Pulse output for electronic shutter O D 2 mA/10 pF

39 SUB_SW SUB voltage control output-1. ADCK input I/O D 2 mA/10 pF

40 SUB_PD SUB voltage control output-2/ XV5 at stripe mode O D 2 mA/10 pF

41 STROB Flash control output. Input Vgate at Hi of pin 61 I/O D 2 mA/10 pF

42 DV

SS

3 General ground for TG (0 V) — D

43 AV

SS

Analog ground (0 V) — A

44 ADC_in AD converter input pin I A

45 BIAS Bias standard resistance — A

46 VRB ADC bottom standard voltage (0.1 µF for GND) — A

47 VRT ADC top standard voltage (0.1 µF for GND) — A

48 VRM ADC middle standard voltage (0.1 µF for GND) — A

49 AV

DD

Analog power supply (3 V) — A

50 BLKC Black level C pin (1000 pF for GND) — A

51 CDS_in CDS input pin I A

52 AV

DD

Analog power supply (3 V) — A

53 BLKFB Black level FB pin (1 µF between BLKFB and BLKSH) I A

54 BLKSH Black level S/H pin O A

55 AV

SS

Analog ground (0 V) — A

56 Test2

H: Normal operation, L: CDS single operation mode

Input 36; PBLK at testing, Input 37; OBP, Input 38; CPDM,

Input 39; ADCK, Input 40; SP2, Input 41; SP1

I D

57 Test1 L: Slave mode, H: Master mode I D

58 DLL_C Analog delay DLL external C pin (100 pF for GND) O A

59 DV

DD

1 Digital power supply (3 V) CDS, PAG, ADC part — D

60 MON Pulse monitor (SP1, SP2, ADCK, OBP, CPDM, PBLK input) O D 2 mA/10 pF

61 41cont

Input STROB = pin 41, Input SUB_SW = pin 39 at Low

Input Vgate = pin 41, Input ADCK = pin 39 at Hi

I D

62 CS Serial data CS at CDS part I D

63 SDATA Input serial data I D

64 SCK Input serial clock I D