HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 24 of 29

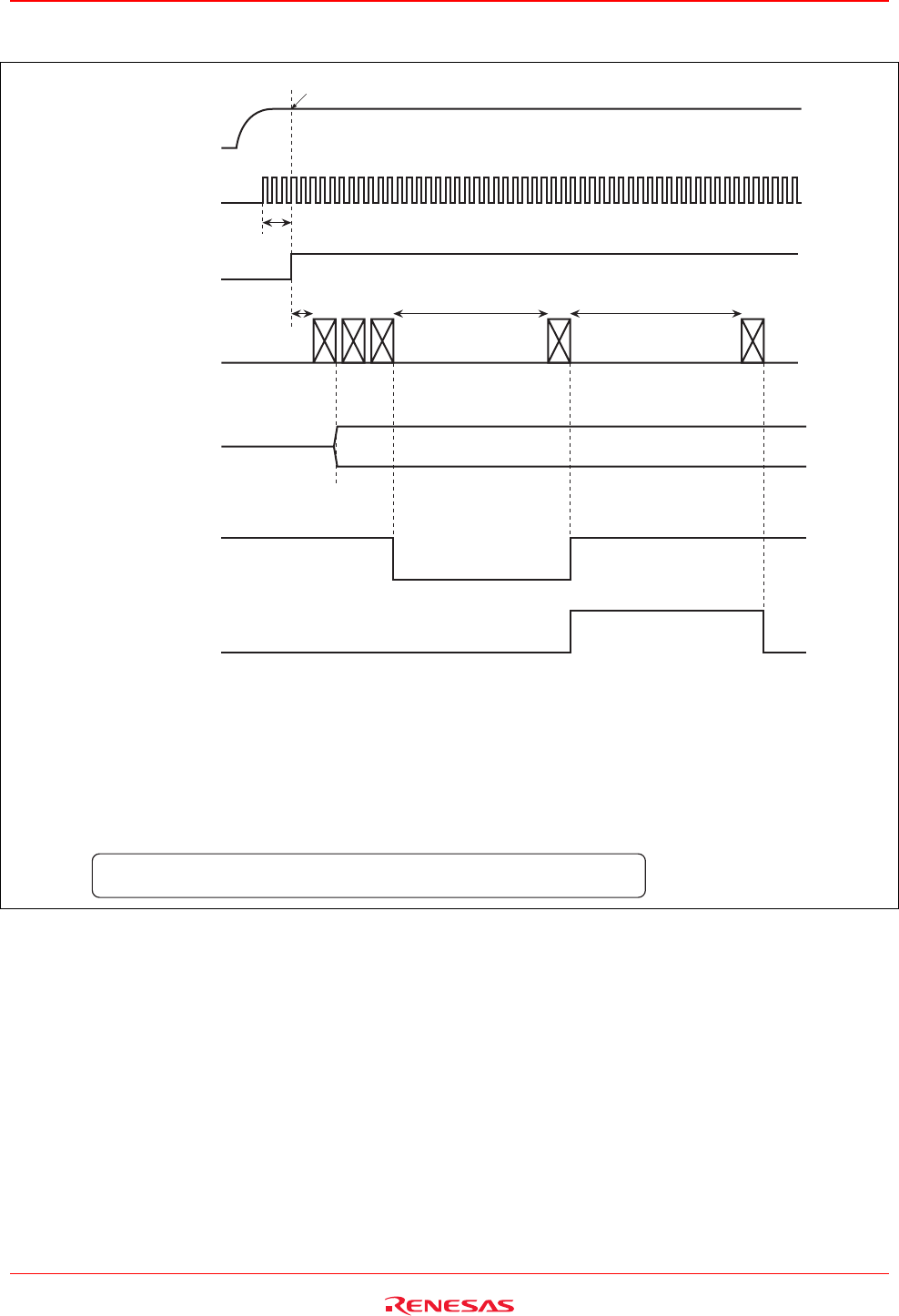

Operation Sequence at Power On

V

DD

(1) Resistor transfer of TG part

(2) DLL data transfer of CDS part

(3) Reset=L of CDS part

(4) Reset=H of CDS part

(5) Other data of CDS part

: Wait more than 6clk after release the hardware Reset and then transfer

the necessary data to TG part.

: Transfer the phase data of RG, SP1, SP2, ADCLK of CDS part.

: Transfer Reset bit = 0 of address H'F2.

: Transfer Reset bit = 1 of address H'F2. (Reset release)

: Transfer the SH_SW_fsel and other PGA.

CLK_in

Hardware

Reset

3clk or more

6clk or more

(1)

2ms or more

(Charge of external C)

40,000ADCLK or more

(offset calibration)

(2) (3) (4)

CDS_Reset = Low

(5)

Note:

At 2 divided mode: ADCLK = 1/2CLK_in

At 3 divided mode: ADCLK = 1/3CLK_in

SP1

SP2

ADCLK

OBP

etc.

RESET bit

Automatic adjustment taking

40,000ADCLK period after

Reset cancellation

∗

Before transfer the Reset bit = 0, TG series pulse need to be settled, so address

H'00 to H'EF of TG part and H'F4 to H7F7 of CDS part should transfer in advance.

HD49335

serial data transfer

Must be stable within the operating

power supply voltage range

Start control

of TG and

camera DSP

A

utomatic offset

calibration

The following describes the above serial data transfer. For details of resistor settings are referred to serial data

function table.