HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 22 of 29

• Address H’F5 sets the DLL delay time and selects the 1/4 phase. Details are on the next page. And D15 of address

H’F8 can switch 2/3 divided mode but ensure that this address data relative to valid/invalid.

D15 of address H’F8 = 0 D15 of address H’F8 = 1

Divided mode 2 divided, 1/4 phase select 3 divided, 1/6 phase select

D0 to D7 of address H’F5 Valid Invalid

D0 to D14 of address H’F8 Invalid Valid

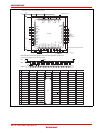

• Phase settings of high speed pulse (address H’F5 to H’F8)

(1) Select the 1/4 phase from figure 13 at 2 divided mode (D15 = 0 of address H’F8).

Select the 1/6 phase from figure 14 at 3 divided mode (D15 = 1 of address H’F8).

·····P_SP1, P_SP2, P_ADCLK, P_RG

(2) Then select the necessary delay time from figure 15.

·····DL_SP1, DL_SP2, DL_RG, DL_ADCLK

RG can be set both of rising / falling edge optionally.

H1

Data = 0

Data = 1

Data = 3

Data = 2

P_SP1

P_SP2

H1

Data = 0

Data = 1

Data = 3

Data = 2

P_ADCLK

P_RG

Figure 13 2 Divided Mode, 1/4 Phase Select (Valid at D15 = 0 of address H’F8)

H1

Data = 5

Data = 2

Data = 3

Data = 4

Data = 1

Data = 0

P_SP1

P_SP2

H1

Data = 0

Data = 3

Data = 4

Data = 5

Data = 2

Data = 1

P_ADCLK

P_RG

Figure 14 3 Divided Mode, 1/6 Phase Select (Valid at D15 = 1 of address H’F8)

Default Value of Each Phases

P_SP1 P_SP2 P_ADCLK P_RG

2 divided mode 1 2 1 0

3 divided mode 0 3 1 5

Note: 50% of duty pulse makes tr, tf of RG by DLL.

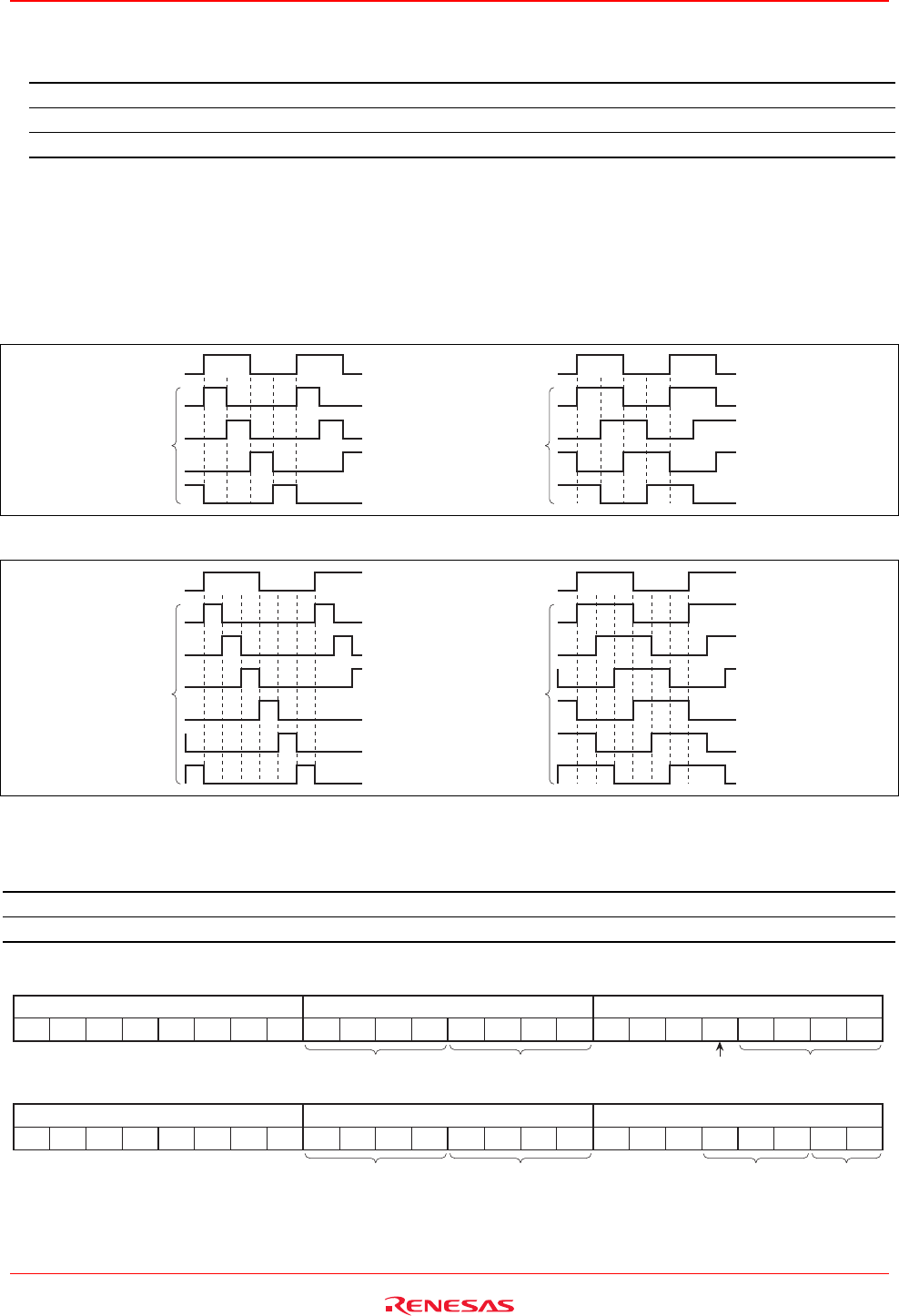

Address STD1[7:0] (L) STD2[15:8] (H)

11110110 D4D3D2D7 D6 D5 D1 D0 D12 D11 D10 D9 D8

DL_SP2 DL_SP1

DL_RG_f

DL_RG_r

DL_ADCLK

CDS_test

Address STD1[7:0] (L) STD2[15:8] (H)

11110111 D4D3D2D7 D6 D5 D1 D0 D12 D11 D10 D9 D8

Dummy

clamp th

Dummy

clamp current