HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 28 of 29

• CDS single operating mode

Pin 56(Test2 = Low) ∗Pin 57 is "Don't care" in this mode.

Serial data when CDS single operation mode are following resister specifications.

(Latch timing specification is same as normal mode)

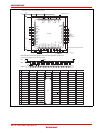

31

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

33

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

16

24 23 22 21 20 19 18 1725262728293032

50 57 58 59 60 61 62 63 6456555453525149

HD49335

1µ

1µ 0.147/6 47/6

1000p 100p

+

PBLK

OBP

CP_DM

ADCK

SP2

SP1

DV

SS

3

AV

SS

ADC_in

BIAS

VRB

VRT

VRM

DV

SS

3

DV

DD

2

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

DV

SS

1,2

DV

DD

3

DV

DD

4

DV

SS

4

DV

SS

4

DV

DD

4

DV

DD

3

Reset

BLKC

CDS_in

AV

DD

BLKFB

BLKSH

AV

SS

Test2

Test1

DLL_C

DV

DD

1

MON

41pin_cont

CS

Sdata

Unit: R: Ω

C: F

AV

DD

SCK

0.147/6

0.1

0.1

0.1

0.1

3.0V

Reset(Normally Hi)

+

+

0.1

33k

∗

Pin changes are not effective with pin61.

ADC_in

47µ

47µ

47µ

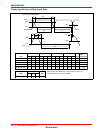

t

INT2

fsck

tsu

CS

SCK

tho

t

INT1

SDATA

D00 D01 D02 D03 D04 D05 D06 D07 D08 D09 D10 D11 D12 D13 D14 D15

D00

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

0

1

0

0

0

0

0

1

0

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

0

0

0

0

0

1

0

1

1

0

1

1

1

0

0

0

1

0

1

1

1

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

0

0

0

1

0

1

0

0

0

0

0

D01

Low

Low

Low

High

Low

Low

Low

High

Low

X

High

High

Low

Low

Low

High

High

Low

High

Low

High

High

High

High

High

Resister 4Resister 3Resister 0 Resister 1 Resister 7Resister 5 Resister 6Resister 2

D02

Test_I1 (0)

D03

D04

D05

D06

D07

D08

D09

D10

D11

D12

D13

D14

D15 Test_I1 (2)

Test_I1 (1)

PGA(0) LSB

X

SLP

Reset

ADSEL

Low:CDSin

High:ADin

LoPwr

STBY

PGA(1)

X

PGA(2)

PGA(3)

PGA(4)

PGA(5)

PGA(6)

PGA(7) MSB

SHSW-fsel(3)

Test_I2 (1)

Test_I2 (0)

Output mode(LINV)

Output mode(MINV)

Output mode(Test0)

SHA-fsel(0)

SHA-fsel(1)

SHSW-fsel(0)

SHSW-fsel(1)

SHSW-fsel(2)

MON(0)

MON(1)

Gray_ts(0)

Gray_ts(2)

Gray_ts(1)

MON(2)

H12Baff(0)

H12Baff(1)

H12Baff(2)

H12Baff(3)

VD latch

Gray1

Gray2

P_SP1(0)

P_SP1(1)

DLL_CK(2)

DLL_current

DLL_CK(3)

P_SP2(0)

P_SP2(1)

P_ADCLK(0)

P_ADCLK(1)

P_RG(0)

P_RG(1)

DLL_CK(0)

DLL_CK(1)

DL_SP1(0)

DL_SP1(1)

DL_ADCLK(2)

CDS_test

DL_ADCLK(3)

DL_SP1(2)

DL_SP1(3)

DL_SP2(0)

DL_SP2(1)

DL_SP2(2)

DL_SP2(3)

DL_ADCLK(0)

DL_ADCLK(1)

DL_RG_r(0)

DL_RG_r(1)

Dummy CP(0)

Dummy CP(2)

Dummy CP(1)

DL_RG_r(2)

DL_RG_r(3)

DL_RG_f(0)

DL_RG_f(1)

DL_RG_f(2)

DL_RG_f(3)

DMCG(0)

DMCG(1)

Clamp(0)

Clamp(1)

Clamp(2)

Clamp(3)

Clamp(4)

HGstop-Hsel(0)

HGstop-Hsel(1)

HGain-Nsel(0)

HGain-Nsel(1)

test

CCD signal input

Serial data input

to

Camera

signal

processor

Low: Normal

High: Sleep

Low: Normal

High: Standby

Low: Normal

High: Low power

Low: Reset

High: Normal