HD49335NP/HNP

Rev.1.0, Feb.12.2004, page 23 of 29

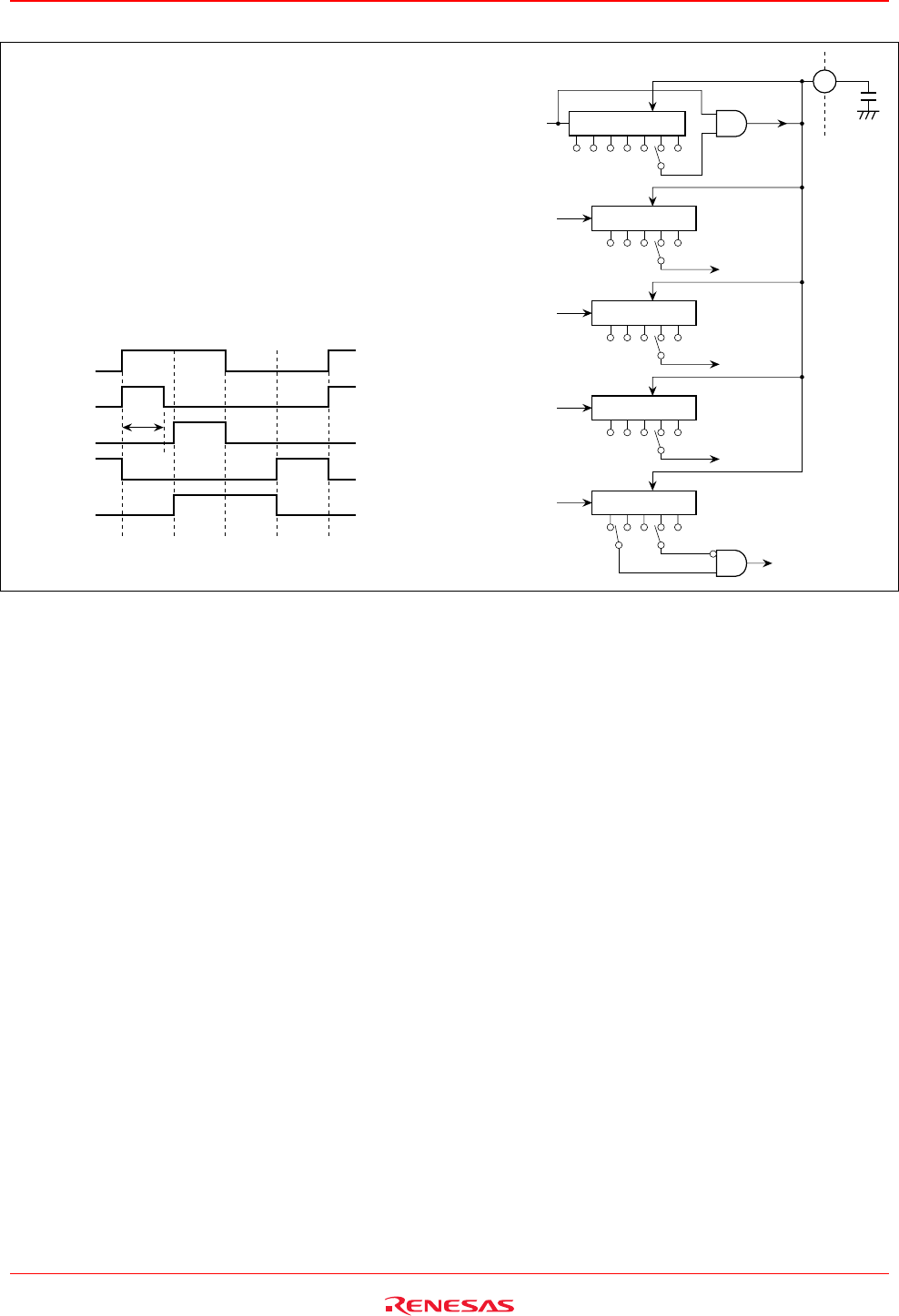

(3) Setting method of DLL

28140

1.

2.

3.

42

∗Default

56

10

H1

DLL step decides the how many divide the 1

cycle of sensor CLK. For reference,

set 1 ns(when 2 ns DLL_current bit = 0,

when 1 set to 1 ns)

Can be set 16 to 64 steps by 4 steps.

Steps = 4 + (4 × N); possible to set N = 3 to 15

Recommended steps is clk_in = when 11 to 14 MHz: H'0E(60 steps)

when 14 to 22MHz: H'09(40 steps)

when 22 to 50MHz: H'1E(60 steps)

when 50 to 72MHz: H'19(40 steps)

Can be change each 4 type of pulse 0 to 15 steps with

1 step. (1 ns or 2 ns divide)

Select the 2 ns divide when sensor CLK is less than

15 MHz.

DL_RG

DL_SP1

DL_ADCLK

DL_SP2

DL_ADCLK

DLL_C

Control voltage

P_ADCLK

AND

PC

DLL = 64 steps

ADCLK(0)

(In phase with H1)

DLL = 15 steps

DL_SP1

P_SP1

DLL = 15 steps

DL_SP2

(Falling)

(Rising)

P_SP2

DLL = 15 steps

ADCLK

(0, 0)

DL_RG

DLL = 15 steps

Figure 15 Analog Delay (DLL) Circuit Block.

• CDS_test (D12 of address H’F6)

It is testing data. Normally set to 0.

• Dummy clamp current (D9 to 8 of address H’F7)

Data = When 0, 1/4 When 1, 1/8

When 2, 1/16 When 3, 1/32

Details are refer to page 12.

• Dummy clamp threshold (D12 to 10 of address H’F7)

Data = When 0, off When 1, +32

When 2, +64 When 3, +96

When 4, +128 When 5, +160

When 6, +192 When 7, +224

Details are refer to page 12.