Functional Overview

2-14 Copyright © 2006 ARM Limited. All rights reserved. ARM DDI 0389B

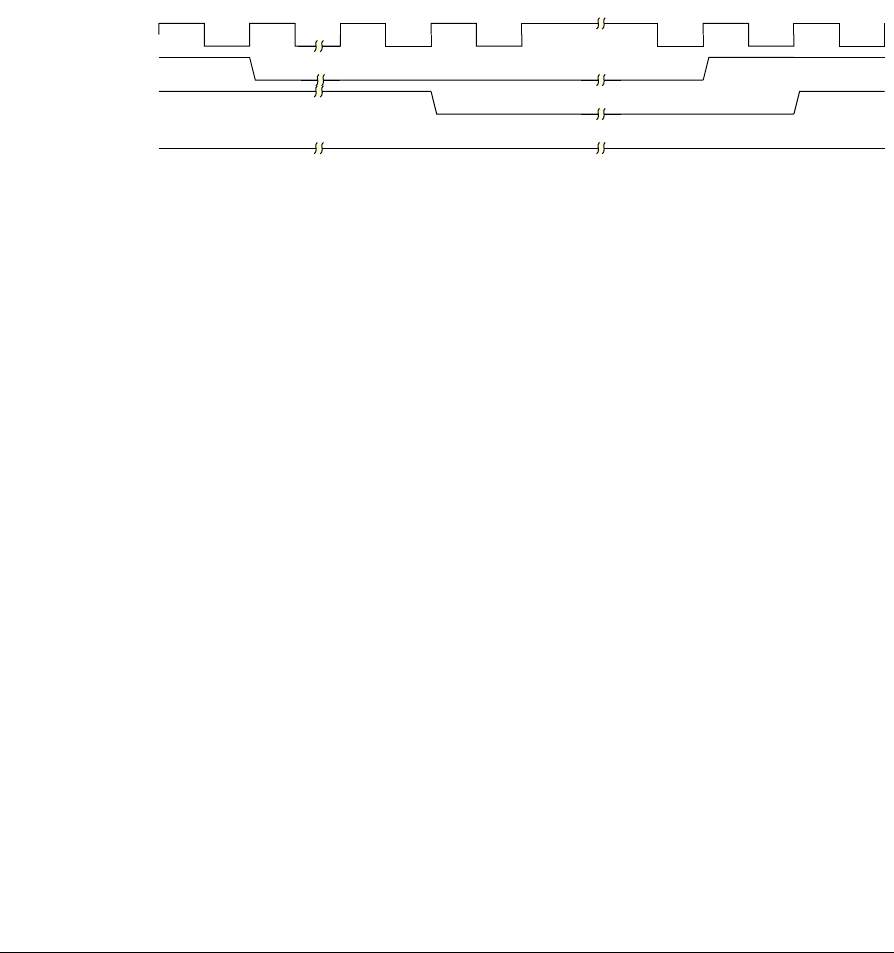

The AHB domain accepts or denies requests based on whether it is busy performing any

transfers. Figure 2-9 shows that static memory controllers always accept requests after

they have performed the required operations to prepare the external memory for the

clock to be switched off.

Figure 2-9 Accepting requests

The low-power request smc_csysreq is driven LOW at time T1. When the memory

controller is happy for the clock to be switched off, the smc_csysack signal is driven

LOW to acknowledge the request, as shown at T2. smc_cactive is driven LOW, so the

system clock controller knows the request has been accepted. When acknowledged, the

system clock controller can disable both the smc_aclk and smc_mclk0 signals.

The two domains have separate interfaces to enable individual handshaking with the

system clock controller. The only usage model is to switch off both domains. Each

individual low-power interface protocol must be observed before all the clocks can be

disabled.

VPFBDFON

VPFBFV\VUHT

VPFBFV\VDFN

VPFBFDFWLYH

7 7 7 7 7