Programmer’s Model

3-6 Copyright © 2006 ARM Limited. All rights reserved. ARM DDI 0389B

3.3 Register descriptions

This section describes the SMC registers.

3.3.1 SMC Memory Controller Status Register at 0x1000

The read-only smc_memc_status Register provides information on the configuration of

the SMC and also the current state of the SMC. This register cannot be read in the Reset

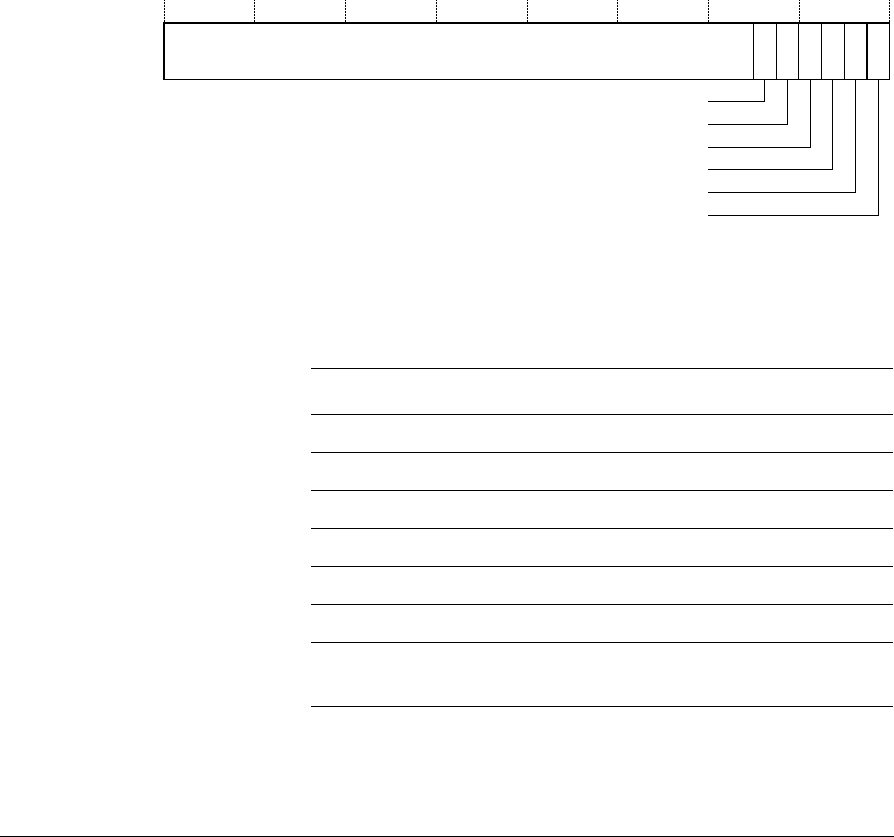

state. Figure 3-6 shows the register bit assignments.

Figure 3-6 smc_memc_status Register bit assignments

Table 3-2 lists the register bit assignments.

VWDWH

LQWBHQ

UDZBLQWBVWDWXV

LQWBVWDWXV

8QGHILQHG

5HVHUYHG

5HVHUYHG

Table 3-2 smc_memc_status Register bit assignments

Bits Name Function

[31:6] - Reserved, read undefined

[5] raw_int_status0 Current raw interrupt status for interface 0

[4] - Reserved, read undefined

[3] int_status0 Current interrupt status for interface 0

[2] - Reserved, read undefined

[1] int_en0 Status of memory interface 0 interrupt enable

[0] state b0 indicates that the SMC is in Ready state

b1 indicates that the SMC is in Low-power state.