AR-B1474 User¡¦s Guide

2-1

2. SYSTEM CONTROLLER

This chapter describes the major structure of the AR-B1474 serial CPU board. The following topics are covered:

l DMA Controller

l Keyboard Controller

l Interrupt Controller

l Serial Port

l Parallel Port

2.1 DMA CONTROLLER

The equivalent of two 8237A DMA controllers are implemented in the AR-B1474 card. Each controller is a four-

channel DMA device that will generate the memory addresses and control signals necessary to transfer

information directly between a peripheral device and memory. This allows high-speed information transfer with less

CPU intervention. The two DMA controllers are internally cascaded to provide four DMA channels for transfers to

8-bit peripherals (DMA1) and three channels for transfers to 16-bit peripherals (DMA2). DMA2 channel 0 provides

the cascade interconnection between the two DMA devices, thereby maintaining IBM PC/AT compatibility.

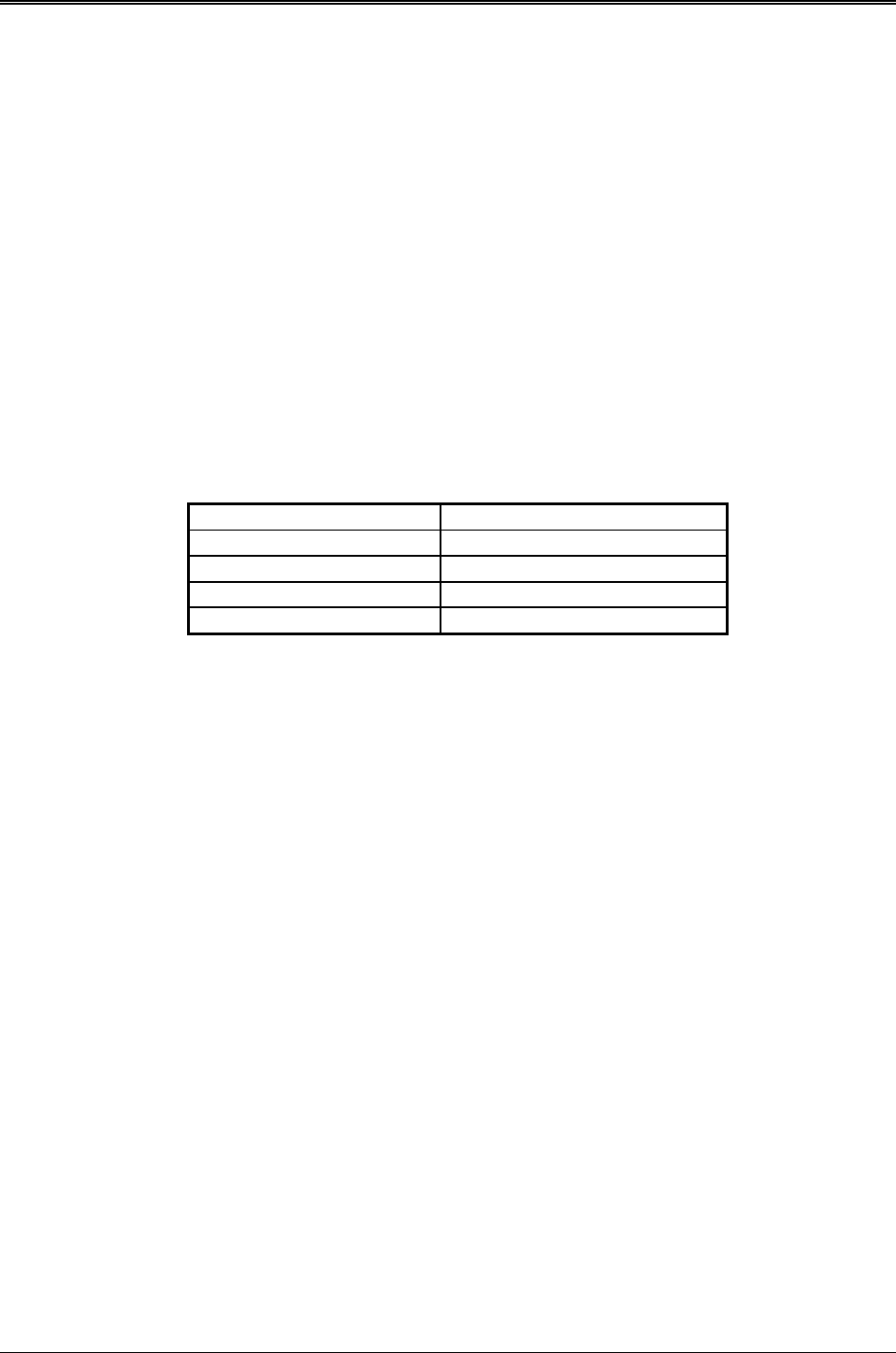

Following is the system information of DMA channels:

DMA Controller 1 DMA Controller 2

Channel 0: Spare Channel 4: Cascade for controller 1

Channel 1: IBM SDLC Channel 5: Spare

Channel 2: Diskette adapter Channel 6: Spare

Channel 3: Spare Channel 7: Spare

Table 2-1 DMA Channel Controller

2.2 KEYBOARD CONTROLLER

The 8042 processor is programmed to support the serial keyboard serial interface. The keyboard controller

receives serial data from the keyboard, checks its parity, translates scan codes, and presents it to the system as a

byte data in its output buffer. The controller can interrupt the system when data is placed in its output buffer, or

wait for the system to poll its status register to determine when data is available.

Data can be written to the keyboard by writing data to the output buffer of the keyboard controller.

Each byte of data is sent to the keyboard controller in series with an odd parity bit automatically inserted. The

keyboard controller is required to acknowledge all data transmissions. Therefore, another byte of data will not be

sent to keyboard controller until acknowledgment is received for the previous byte sent. The “output buffer full”

interrupt may be used for both send and receive routines.