www.ti.com

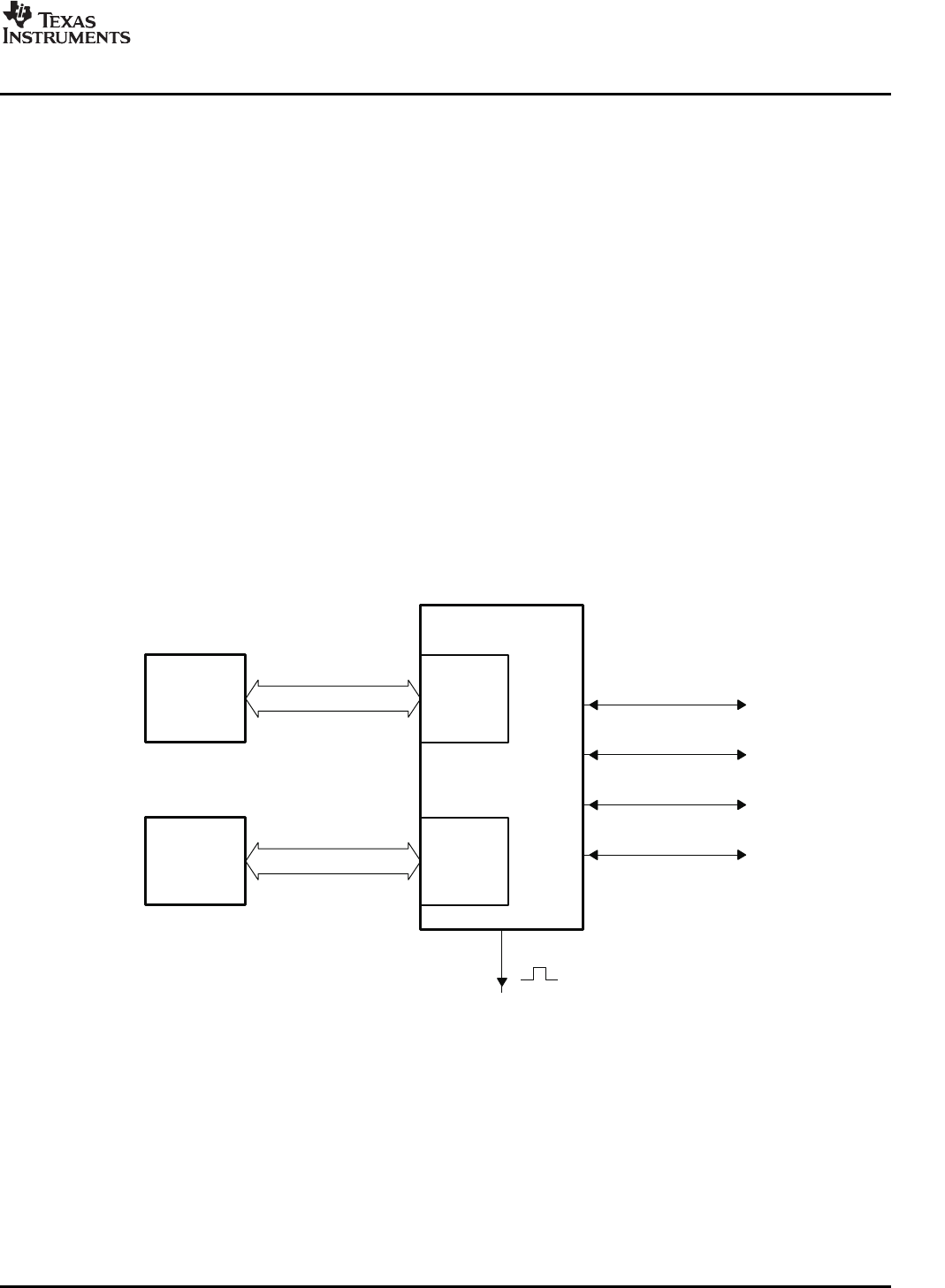

1.3FunctionalBlockDiagram

Slave

config

bus

Interface

Master

config

Interface

bus

VLYNQmodule

VLYNQregister

access

CPU/EDMA initiated

transfersto

remotedevice

Offchip

(remote)

deviceaccess

System

CPU/EDMA

memory

System

VLYNQ_SCRUN

VLYNQ_CLOCK

VLYNQ_RXD[3:0]

VLYNQ_TXD[3:0]

INT55

interruptcontroller

VLQINT

1.4IndustryStandard(s)ComplianceStatement

Introduction

•SymmetricOperations

–Transmit(TX)pinsonthefirstdeviceconnecttothereceive(RX)pinsontheseconddeviceand

vice-versa.

–Datapinwidthsareautomaticallydetectedafterreset

–Re-requestpackets,responsepackets,andflowcontrolinformationareallmultiplexedandsent

acrossthesamephysicalpins.

–Supportsbothhost/peripheralandpeer-to-peercommunicationmodels

•Simpleblockcodepacketformatting(8b/10b)

•Supportsin-bandandflowcontrol

–Noextrapinsareneeded

–Allowsthereceivertomomentarilythrottlethetransmitterbackwhenoverflowisabouttooccur

–Usesthespecialbuilt-inblockcodecapabilitytointerleaveflowcontrolinformationseamlesslywith

userdata

•Automaticpacketformattingoptimizations

•Internalloopbackmodesareprovided

•ConnectstolegacyVLYNQdevices

Figure1showsafunctionalblockdiagramoftheVLYNQport.

Figure1.VLYNQPortFunctionalBlockDiagram

VLYNQisaninterfacedefinedbyTexasInstrumentsanddoesnotconformtoanyotherindustrystandard.

SPRU938B–September2007VLYNQPort9

SubmitDocumentationFeedback