www.ti.com

TVP5158EVM Evaluation Procedures

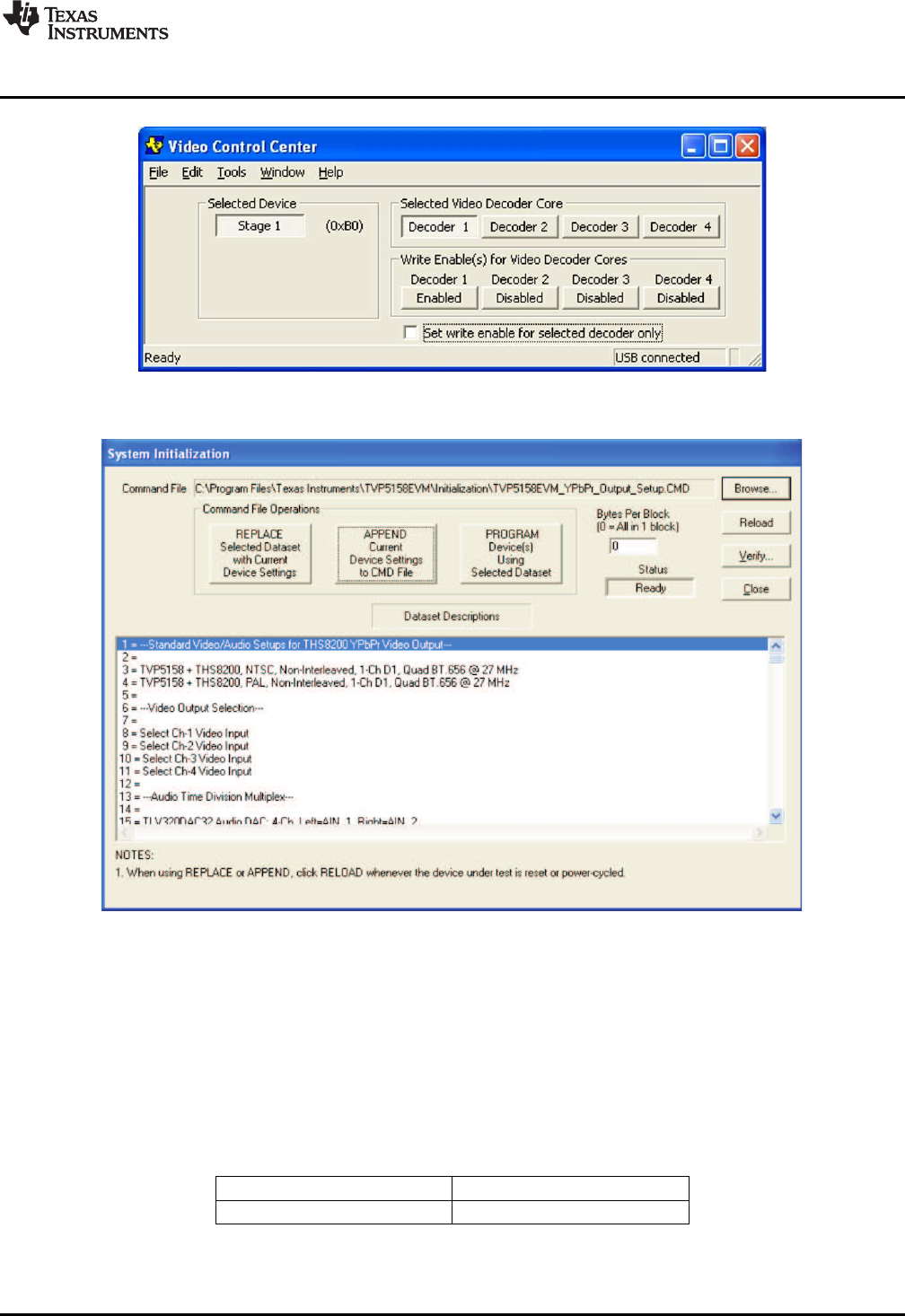

Figure 12. VCC Main Window - Set for Communication to All Decoders

Figure 13. System Initialization for Analog Component YPbPr Video Output

7.2 Evaluation Using the DaVinci HD EVM

7.2.1 Setting DM6467 ARM and DDR2 Memory Clock Rates

For maximum performance, in a system using DM6467 and TVP5158(s) in the line-interleaved video

modes, the DM6467 clock frequencies should be set as specified in Table 7.

Table 7. Recommended DM6467 Clock Frequencies

ARM Clock 675 MHz

DDR2 Memory Clock 324 MHz

(1)

(1)

DaVinci HD EVM assembly revision F or later is required.

19

SLEU108–November 2009 TVP5158 Evaluation Module

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated