5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

DVO_A_0

DVO_A_1

DVO_A_2

DVO_A_3

DVO_A_4

DVO_A_5

DVO_A_6

DVO_A_7

DVO_D_0

DVO_D_1

DVO_D_2

DVO_D_3

DVO_D_4

DVO_D_5

DVO_D_6

DVO_D_7

DVO_C_0

DVO_C_1

DVO_C_2

DVO_C_3

DVO_C_4

DVO_C_5

DVO_C_6

DVO_C_7

DVO_B_0

DVO_B_1

DVO_B_2

DVO_B_3

DVO_B_4

DVO_B_5

DVO_B_6

DVO_B_7

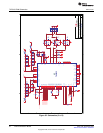

OCLK_P

OCLK_N

OCLK_N_5158

OCLK_P3_OUT

OCLK_N_OUT

LRCLK_R

SD_CO

BCLK_R

TVP5158_INTREQ

OSC_OUT

DVO_BOUT_0

DVO_BOUT_1

DVO_BOUT_2

DVO_BOUT_3

DVO_BOUT_4

DVO_BOUT_5

DVO_BOUT_6

DVO_BOUT_7

I2C_SDA

I2C_SCL

OCLK_N

BCLK_CI

SD_CI

LRCLK_CI

DVO_D_0

DVO_D_1

DVO_D_2

DVO_D_3

DVO_D_4

DVO_D_5

DVO_D_6

DVO_D_7

I2C_SDA

I2C_SCL

CLKIN_CAS

INTREQ_2nd

DVO_C_0

DVO_C_1

DVO_C_2

DVO_C_4

DVO_C_3

DVO_C_5

DVO_C_6

DVO_C_7

DVO_A_0

DVO_A_1

DVO_A_2

DVO_A_3

DVO_A_4

DVO_A_5

DVO_A_6

DVO_A_7

DVO_B_0

DVO_B_1

DVO_B_2

DVO_B_3

DVO_B_4

DVO_B_5

DVO_B_6

DVO_B_7

OCLK_N

OCLK_P

OCLK_N_OUT

DVO_BOUT_3

DVO_BOUT_4

DVO_BOUT_5

DVO_BOUT_6

DVO_BOUT_7

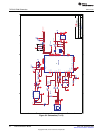

DVO_AOUT_0

DVO_AOUT_1

DVO_AOUT_2

DVO_AOUT_3

DVO_AOUT_4

DVO_AOUT_5

DVO_AOUT_6

DVO_AOUT_7

OCLK_P_OUT

DVO_BOUT_1

DVO_BOUT_2

DVO_BOUT_0

DVO_A2_OUT_0

DVO_A2_OUT_1

DVO_A2_OUT_2

DVO_A2_OUT_3

DVO_A2_OUT_4

DVO_A2_OUT_5

DVO_A2_OUT_6

DVO_A2_OUT_7

DVO_A3_OUT_0

DVO_A3_OUT_1

DVO_A3_OUT_2

DVO_A3_OUT_3

DVO_A3_OUT_4

DVO_A3_OUT_5

DVO_A3_OUT_6

DVO_A3_OUT_7

DVO_A3_OUT_0

DVO_A3_OUT_1

DVO_A3_OUT_2

DVO_A3_OUT_3

DVO_A3_OUT_4

DVO_A3_OUT_5

DVO_A3_OUT_6

DVO_A3_OUT_7

OCLK_P2_OUT

OCLK_P3_OUT

+3.3VD

BCLK_R

LRCLK_R

SD_CO

TVP5158_INTREQ

OSC_OUT

BCLK_CI

LRCLK_CI

SD_CI

I2C_SCL

I2C_SDA

CLKIN_CAS

INTREQ_2nd

DVO_AOUT_2

DVO_AOUT_3

DVO_AOUT_4

DVO_AOUT_5

DVO_AOUT_6

DVO_AOUT_7

DVO_BOUT_2

DVO_BOUT_3

DVO_BOUT_4

DVO_BOUT_5

DVO_BOUT_6

DVO_BOUT_7

DVO_BOUT_1

DVO_AOUT_0

OCLK_P_OUT

DVO_AOUT_1

DVO_BOUT_0

DVO_A2_OUT_7

DVO_A2_OUT_0

DVO_A2_OUT_1

DVO_A2_OUT_2

DVO_A2_OUT_3

DVO_A2_OUT_4

DVO_A2_OUT_5

DVO_A2_OUT_6

OCLK_P2_OUT

Title

Size DocumentNumber

Rev

Date:

Sheet

of

TVP5158 EVM

VIDEO INPUT

1.3

B

1

8

Thursday, October 08,2009

Title

Size DocumentNumber

Rev

Date:

Sheet

of

TVP5158 EVM

VIDEO INPUT

1.3

B

1

8

Thursday, October 08,2009

Title

Size DocumentNumber

Rev

Date:

Sheet

of

TVP5158 EVM

VIDEO INPUT

1.3

B

1

8

Thursday, October 08,2009

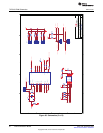

Place R50, R51, R52 and R53 close to J1

The pin assignment in the footprints of J2 and J3 needs to be mirror rotated.

INTREQ_2nd from 2nd Stage

TVP5158 to DaVinci HD GPIO

Place R54, R55, R56 and R57 close to J1

TO J2

TO THS8200

TO J9

TO J9

RP3 0RP3 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

C72

0.1uF

C72

0.1uF

R47

2.2K

R47

2.2K

R54

37.4

R54

37.4

R49

0

R49

0

R51

75

R51

75

R59 0R59 0

C70

0.1uF

C70

0.1uF

R58

1.8K

R58

1.8K

RP1 0RP1 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

RP4 0RP4 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

J1B

RCA_Octal_stack

J1B

RCA_Octal_stack

3

10

9

11

12

4

R48

0

R48

0

R52

75

R52

75

R56

37.4

R56

37.4

U1A

TVP5158

U1A

TVP5158

DVO_A_0

78

DVO_A_1

77

DVO_A_2

75

DVO_A_3

74

DVO_A_4

72

DVO_A_5

71

DVO_A_6

69

DVO_A_7

68

DVO_B_0

63

DVO_B_1

62

DVO_B_2

60

DVO_B_3

59

DVO_B_4

57

DVO_B_5

56

DVO_B_6

54

DVO_B_7

53

OCLK_P

51

DVO_C_0

46

DVO_C_1

45

DVO_C_2

43

DVO_C_3

42

DVO_C_4

40

DVO_C_5

39

DVO_C_6

37

DVO_C_7

36

DVO_D_0

31

DVO_D_1

30

DVO_D_2

28

DVO_D_3

27

DVO_D_4

25

DVO_D_5

24

DVO_D_6

22

DVO_D_7

21

OCLK_N/CLKIN

50

VIN_1_P

108

VIN_1_N

109

VIN_2_P

112

VIN_2_N

113

VIN_3_P

121

VIN_3_N

122

VIN_4_P

125

VIN_4_N

126

REXT_2K

116

C71

0.1uF

C71

0.1uF

U9

SN74AVC16827DGVR

U9

SN74AVC16827DGVR

1A1

55

1A2

54

1A3

52

1A4

51

1A5

49

1A6

48

1A7

47

1A8

45

1A9

44

1A10

43

2A1

42

2A2

41

2A3

40

2A4

38

2A5

37

2A6

36

2A7

34

2A8

33

2A9

31

2A10

30

1Y1

2

1Y2

3

1Y3

5

1Y4

6

1Y5

8

1Y6

9

1Y7

10

1Y8

12

1Y9

13

1Y10

14

2Y1

15

2Y2

16

2Y3

17

2Y4

19

2Y5

20

2Y6

21

2Y7

23

2Y8

24

2Y9

26

2Y10

27

1OE1

1

2OE1

28

1OE2

56

2OE2

29

Gnd1

4

Gnd2

11

Gnd3

18

Gnd4

25

Gnd5

53

Gnd6

46

Gnd7

39

Gnd8

32

VCC1

7

VCC2

22

VCC3

50

VCC4

35

R55

37.4

R55

37.4

RP2 0RP2 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

J2

Cascade Output

J2

Cascade Output

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

31

31

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

33

33

34

34

C73

0.1uF

C73

0.1uF

R50

75

R50

75

R105

0

R105

0

J3

Cascade Input

J3

Cascade Input

1

1

3

3

5

5

7

7

9

9

11

11

13

13

15

15

17

17

19

19

21

21

23

23

25

25

27

27

29

29

31

31

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

18

20

20

22

22

24

24

26

26

28

28

30

30

32

32

33

33

34

34

C76

0.1uF

C76

0.1uF

C74

0.1uF

C74

0.1uF

C77

0.1uF

C77

0.1uF

R53

75

R53

75

C75

0.1uF

C75

0.1uF

R57

37.4

R57

37.4

R104

0

R104

0

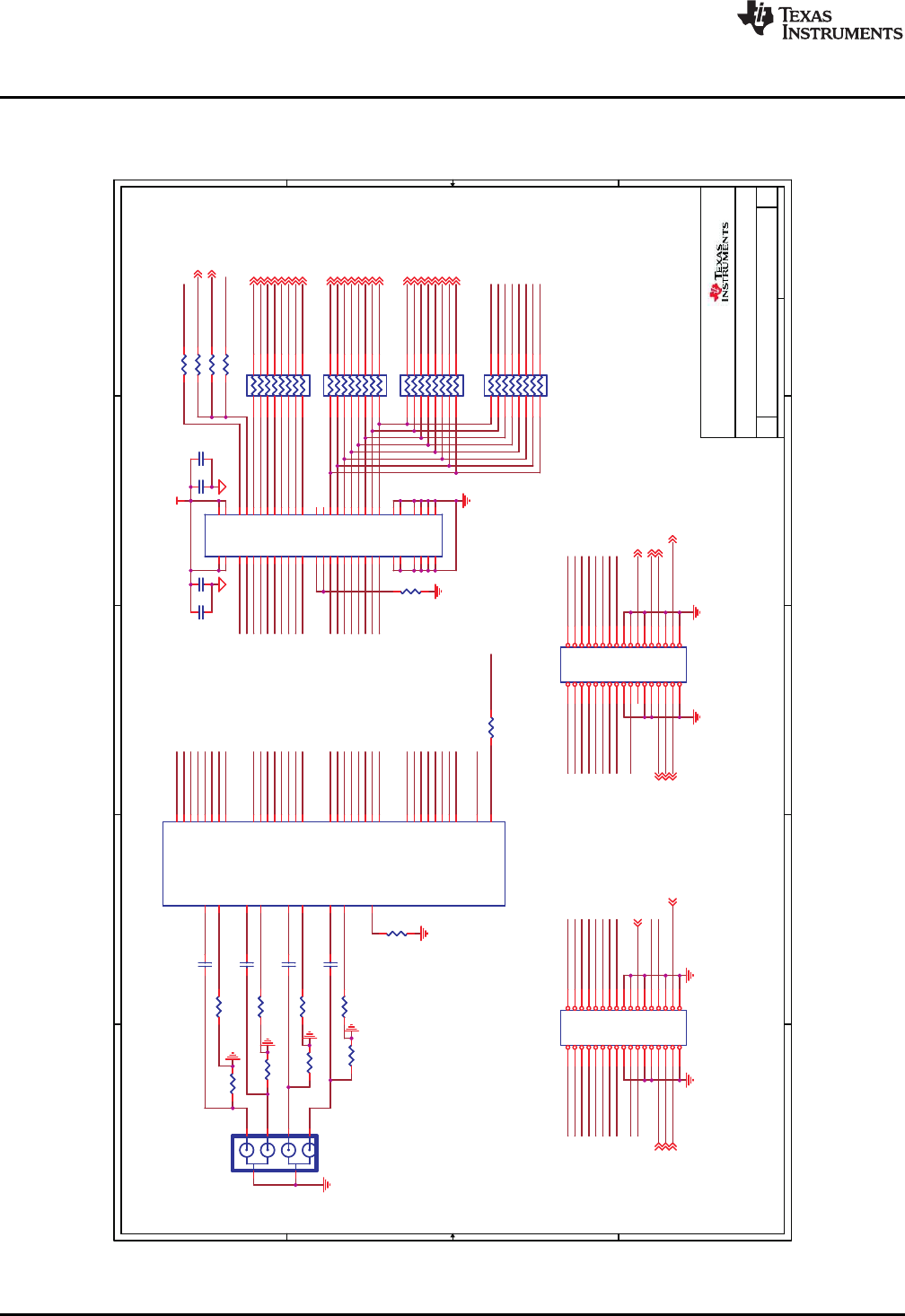

TVP5158 EVM Schematics

www.ti.com

10 TVP5158 EVM Schematics

This section contains the TVP5158EVM schematics.

Figure 28. Schematics (1 of 8)

38

TVP5158 Evaluation Module SLEU108–November 2009

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated