Toshiba Corporation Digital Media Network Company

Page 124 of 153

© 2003, Copyright TOSHIBA Corporation All Rights Reserved

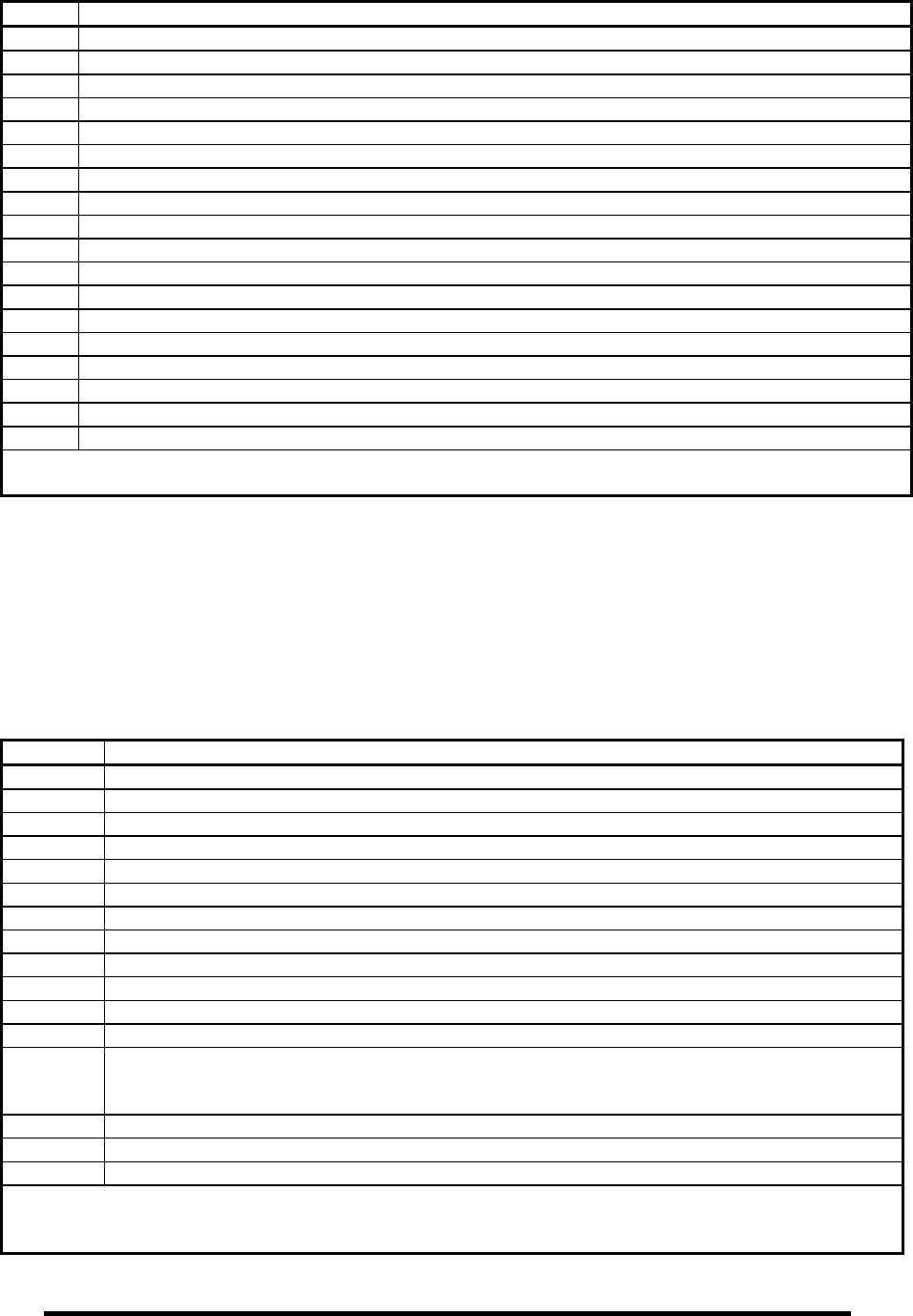

Command data structure

Byte Descriptions

n Content of the Device Control register when the Command register was written.

N+1 Content of the Features register (7:0) when the Command register was written. (see note)

n+2 Content of the Features register (15:8) when the Command register was written.

N+3 Content of the Sector Count register (7:0) when the Command register was written.

N+4 Content of the Sector Count register (15:8) when the Command register was written.

N+5 Content of the LBA Low register (7:0) when the Command register was written.

N+6 Content of the LBA Lowregister (15:8) when the Command register was written.

N+7 Content of the LBA Mid register (7:0) when the Command register was written.

N+8 Content of the LBA Mid register (15:8) when the Command register was written.

N+9 Content of the LBA High register (7:0) when the Command register was written.

N+10 Content of the LBA High register (15:8) when the Command register was written.

N+11 Content of the Device/Head register when the Command register was written.

N+12 Content written to the Command register.

N+13 Reserved

n+14 Timestamp (least significant byte)

n+15 Timestamp (next least significant byte)

n+16 Timestamp (next most significant byte)

n+17 Timestamp (most significant byte)

NOTE - bits (7:0) refer to the most recently written contents of the register. Bits (15:8) refer to the

contents of the register prior to the most recent write to the register.

Timestamp shall be the time since power-on in milliseconds when command acceptance occurred. This

timestamp may wrap around.

11.8.43.2.3.2 Error data structure

The error data structure shall contain the error description of the command for which an error was reported as

described in the following table. If the error was logged for a hardware reset, the content of bytes n+1 through

n+11 shall be vendor specific and the remaining bytes shall be as defined in the following table.

Error data structure

Byte Descriptions

n Reserved

n+1 Content of the Error register after command completion occurred.

N+2 Content of the Sector Count register (7:0) after command completion occurred. (see note)

n+3 Content of the Sector Count register (15:8) after command completion occurred. (see note)

n+4 Content of the LBA Low register (7:0) after command completion occurred.

N+5 Content of the LBA Low register (15:8) after command completion occurred.

N+6 Content of the LBA Mid register (7:0) after command completion occurred.

N+7 Content of the LBA Mid register (15:8) after command completion occurred.

N+8 Content of the LBA High register (7:0) after command completion occurred.

N+9 Content of the LBA High register (15:8) after command completion occurred.

N+10 Content of the Device/Head register after command completion occurred.

N+11 Content written to the Status register after command completion occurred.

N+12

through

n+30

Extended error information

n+31 State

n+32 Life timestamp (least significant byte)

n+33 Life timestamp (most significant byte)

NOTE - bits (7:0) refer to the contents if the register were read with bit 7 of the Device Control register

cleared to zero. Bits (15:8) refer to the contents if the register were read with bit 7 of the Device

Control register set to one.