S1854 Trinity 400

47

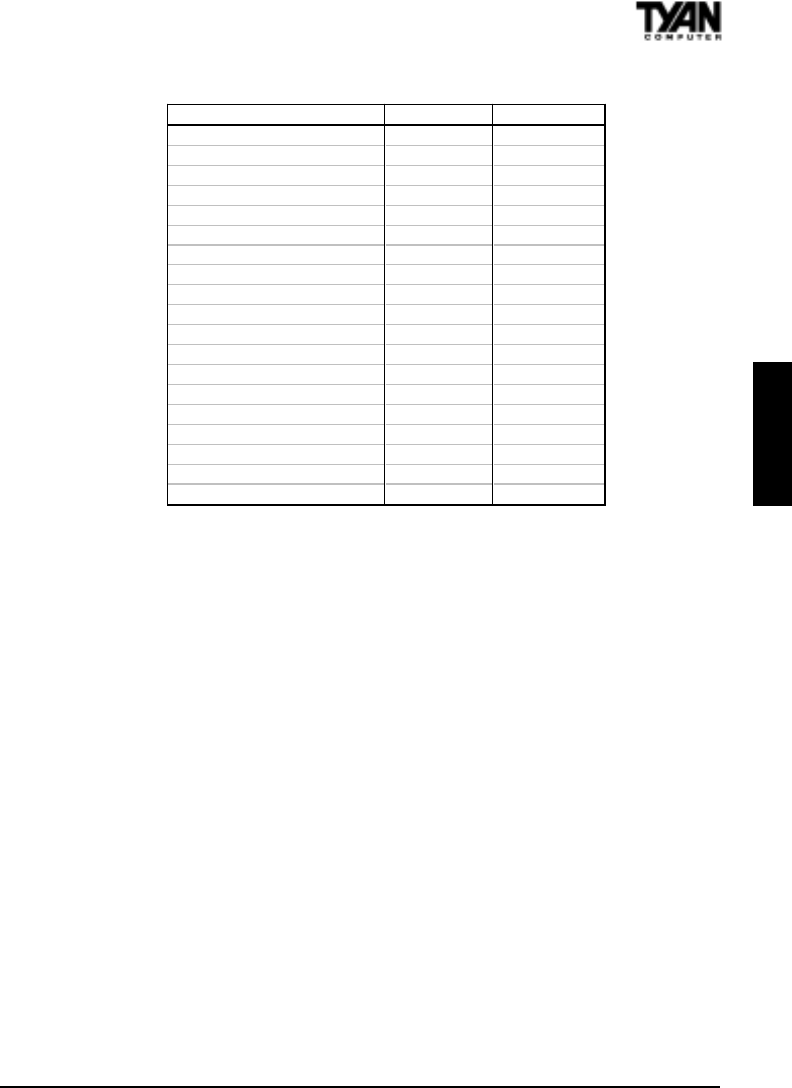

Chipset Features Setup - Default Settings Chart

Memory Hole

This option specifies the location of an area of memory that cannot be

addressed on the ISA bus. The settings are Disabled, 512KB-64KB, or 15MB-

16MB.

P2C/C2P Concurrency

By enabling this function the PCI/AGP Master to CPU Cycle can be concur-

rent if the Host CPU is performing R/W access to the PCI or slave devices.

Fast Read Write turn-around

If Enabled, it reduces the turn around time for a memory read is followed by a

memory write consecutively.

CPU IOQ Size

This setting controls the In Order Que of the CPU with the chipset, setting it

to higher levels yields higher performace, although system may become

unstable. Default is set to 1 Level.

System BIOS Cacheable

If Enabled, results in better system performance by permitting caching of the

system BIOS ROM at F0000h-FFFFFh. Any program which tries to write to this

memory area, however, may cause a system error.

BIOS

Setting Option BIOS Default Setup Default

Bank 0/1 DRAM Timing SDRAM 10ns SDRAM 10ns

Bank 2/3 DRAM Timing SDRAM 10ns SDRAM 10ns

Bank 4/5 DRAM Timing SDRAM 10ns SDRAM 10ns

SDRAM Cycle Length 3 3

DRAM Clock Host CLK 33M Host CLK-33M

Memory Hole Disabled Disabled

P2C/C2P Concurrency Enabled Enabled

Fast R-W Turn Around Disabled Enabled

CPU IOQ Size 1 Level 1 Level

System BIOS Cacheable Disabled Enabled

Video RAM Cacheable Disabled Enabled

AGP Aperture Size 64M 64M

AGP Driving Control Manual Manual

AGP Driving Value EC EC

AGP-4x Mode Disabled Disabled

OnChip USB Enabled Enabled

USB Keyboard Support Disabled Disabled

Auto Detect DIMM/PC2 CLK Enabled Disabled

CPU Clock/Spread Spectrum Default Default