S1854 Trinity 400

57

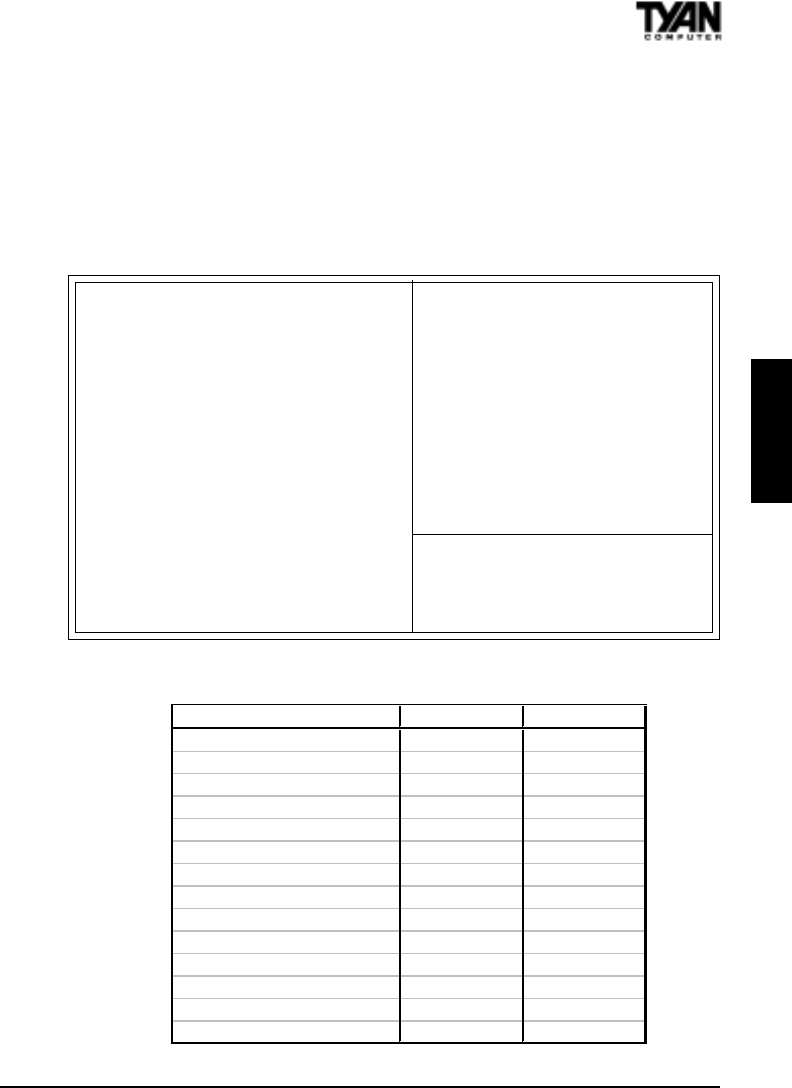

Integrated Peripherals

Note: This chapter describes all fields offered by Award Software in this

screen. Your system board designer may omit or modify some fields.

Integrated Peripherals - Default Settings Chart

OnChip IDE Channel 0 : Enabled UART Mode Select : Normal

OnChip IDE Channel 1 : Enabled

IDE Prefetch Mode : Disabled

IDE Primary Master PIO : Auto Onboard Parallel Port : 378/IRQ7

IDE Primary Slave PIO : Auto Onboard Parallel Mode : SPP

IDE Secondary Master PIO : Auto

IDE Secondary Slave PIO : Auto

IDE Primary Master UDMA : Disabled PWRON After PWR Fail : Off

IDE Primary Slave UDMA : Disabled

IDE Secondary Master UDMA : Disabled

IDE Secondary Slave UDMA : Disabled

Init Display First : AGP

Power On Function : Button Only

KBC Input Clock : 8MHz

Onboard FDD Controller : Enabled

Onboard Serial Port 1 : 3F8/IRQ4

Onboard Serial Port 2 : 2F8/IRQ3

ROM PCI/ISA BIOS (TYAN1854)

INTEGRATED PERIPHERALS

AWARD SOFTWARE, INC.

ESC : Quit ↑↓ →← : Select Item

F1 : Help PU/PD/+/- : Modify

F5 : Old Values (Shift)F2 : Color

F6 : Load BIOS Defaults

F7 : Load Setup Defaults

BIOS

Setting Option BIOS Default Setup Default

OnChip IDE First Channel Enabled Enabled

OnChip IDE Second Channel Enabled Enabled

IDE Prefetch Mode Disabled Enabled

IDE Primary Mas ter PIO Auto Auto

IDE Primary Slave PIO Auto Auto

IDE Secondary Master PIO Auto Auto

IDE Secondary Slave PIO Auto Auto

IDE Primary Master UDMA Disabled Auto

IDE Primary Slave UDMA Disabled Auto

IDE Secondary Master UDMA Disabled Auto

IDE Secondary Slave UDMA Disabled Auto

Init Dis play First AGP AGP

KBC Input Clock 8 MHz 8 MHz

Onboard FDC Controller Enabled Enabled