SP601 Hardware User Guide www.xilinx.com 19

UG518 (v1.1) August 19, 2009

Detailed Description

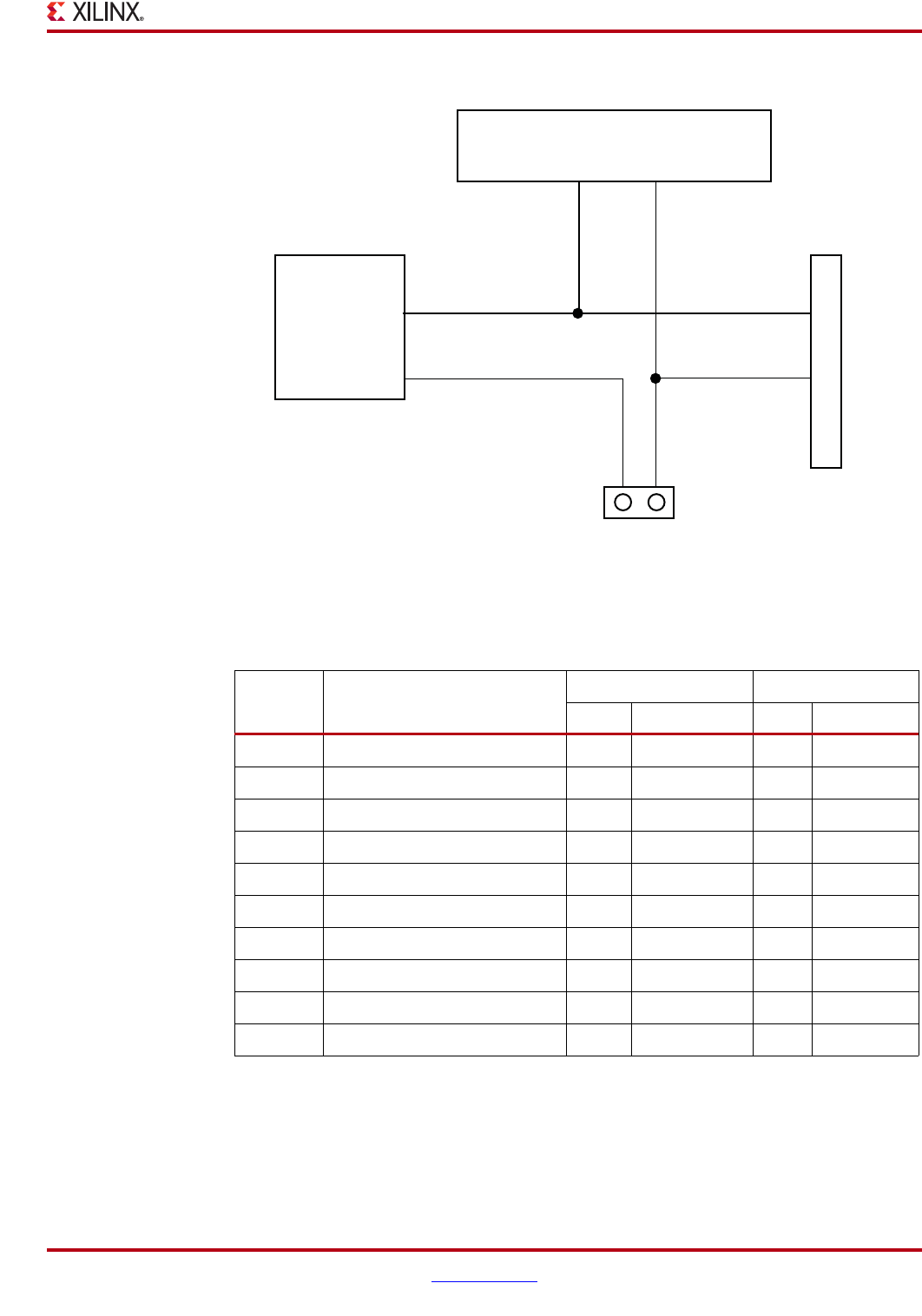

X-Ref Target - Figure 1-7

Figure 1-7: SPI Flash Interface Topology

Table 1-6: SPI x4 Memory Connections

FPGA U1

Pin

Schematic Netname

SPI MEM U17 SPI HDR J12

Pin # Pin Name Pin # Pin Name

V2 FPGA_PROG_B 1

V14 FPGA_D2_MISO3 1 IO3_HOLD_B 2

T14 FPGA_D1_MISO2_R 9 IO2_WP_B 3

V3 SPI_CS_B 4 TMS

T13 FPGA_MOSI_CSI_B_MISO0 15 DIN 5 TDI

R13 FPGA_D0_DIN_MISO_MISO1 8 IO1_DOUT 6 TDO

R15 FPGA_CCLK 16 CLK 7 TCK

8GND

9 VCC3V3

J15.2 SPIX4_CS_B 7 CS_B

U1

FPGA SPI INTERFACE

U17

J12

SPI X4

FLASH

MEMORY

WINBOND

W25Q64VSFIG

SPI PROGRAM

HEADER

SPI SELECT

JUMPER

ON = SPI X4 U17

OFF = SPI EXT. J12

SPIX4_CS_B

DIN,DOUT,CCLK

SPI_CS_B

2

J15

1

UG518_07_070809