26 www.xilinx.com SP601 Hardware User Guide

UG518 (v1.1) August 19, 2009

Chapter 1: SP601 Evaluation Board

References

Technical information on the Silicon Labs CP2103GM and the VCP drivers can be found on

their website at https://www.silabs.com/Pages/default.aspx

.

In addition, see some of the Xilinx UART IP specifications at:

•

http://www.xilinx.com/support/documentation/ip_documentation/opb_uartlite.pdf

• http://www.xilinx.com/support/documentation/ip_documentation/xps_uartlite.pdf

• http://www.xilinx.com/support/documentation/ip_documentation/xps_uart16550.pdf

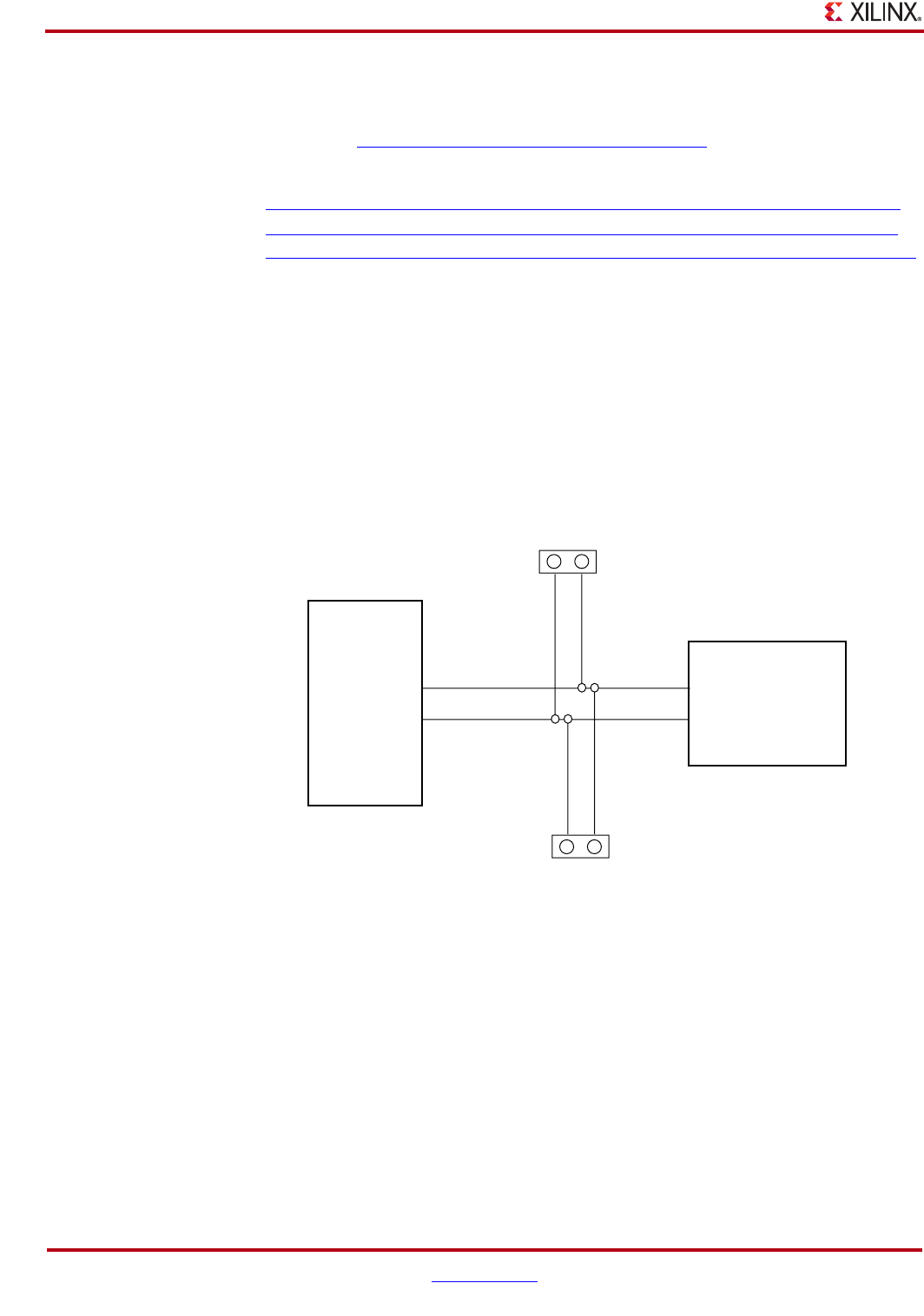

7. IIC Bus

The SP601 IIC bus hosts four items:

• FPGA U1 IIC interface

• 2-pin IIC external access header

• 8-Kb NV Memory

• VITA 57.1 FMC Connector J1

The SP601 IIC bus topology is shown in Figure 1-13.

The IIC Bus on the SP601 provides access to a 2-pin header, the onboard 8-Kb EEPROM,

and the VITA 57.1 FMC interface. The user must ensure there are no IIC address conflicts

with the onboard EEPROM address when attaching additional IIC devices via FMC or the

IIC 2-pin header. Note that FMC Mezzanine cards are designed with 2-Kb IIC EEPROMs

and will not conflict with the Carrier Card (SP601) 8-Kb EEPROM address range. This is

because 2-Kb EEPROMs reside below the 8-Kb EEPROM space. See the VITA 57.1

specification along with any IIC 2-Kbit EEPROM data sheet for more details.

X-Ref Target - Figure 1-13

Figure 1-13: IIC Bus Topology

FPGA IIC

INTERFACE

U1

IIC_SDA_MAIN

IIC_SCL_MAIN

2

C30 C31

1

J16

J1

IIC EXTERNAL

ACCESS

CONNECTOR

VITA 57.1

FMC-LPC

U7

ST MICRO

M24 C08-WDW6TP

UG518_13_070809

Address range

54-56

0b1010100-

0b1010110

FMC-LPC

GA0=1

GA1=0