52 www.xilinx.com SP601 Hardware User Guide

UG518 (v1.1) August 19, 2009

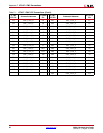

Appendix D: SP601 Master UCF

NET "DDR2_LDQS_P" LOC = "L4";

NET "DDR2_ODT" LOC = "K6";

NET "DDR2_RAS_B" LOC = "L5";

NET "DDR2_UDM" LOC = "K4";

NET "DDR2_UDQS_N" LOC = "P1";

NET "DDR2_UDQS_P" LOC = "P2";

NET "DDR2_WE_B" LOC = "E3";

NET "FLASH_A0" LOC = "K18";

NET "FLASH_A1" LOC = "K17";

NET "FLASH_A2" LOC = "J18";

NET "FLASH_A3" LOC = "J16";

NET "FLASH_A4" LOC = "G18";

NET "FLASH_A5" LOC = "G16";

NET "FLASH_A6" LOC = "H16";

NET "FLASH_A7" LOC = "H15";

NET "FLASH_A8" LOC = "H14";

NET "FLASH_A9" LOC = "H13";

NET "FLASH_A10" LOC = "F18";

NET "FLASH_A11" LOC = "F17";

NET "FLASH_A12" LOC = "K13";

NET "FLASH_A13" LOC = "K12";

NET "FLASH_A14" LOC = "E18";

NET "FLASH_A15" LOC = "E16";

NET "FLASH_A16" LOC = "G13";

NET "FLASH_A17" LOC = "H12";

NET "FLASH_A18" LOC = "D18";

NET "FLASH_A19" LOC = "D17";

NET "FLASH_A20" LOC = "G14";

NET "FLASH_A21" LOC = "F14";

NET "FLASH_A22" LOC = "C18";

NET "FLASH_A23" LOC = "C17";

NET "FLASH_A24" LOC = "F16";

NET "FLASH_CE_B" LOC = "L17";

NET "FLASH_D3" LOC = "U5";

NET "FLASH_D4" LOC = "V5";

NET "FLASH_D5" LOC = "R3";

NET "FLASH_D6" LOC = "T3";

NET "FLASH_D7" LOC = "R5";

NET "FLASH_OE_B" LOC = "L18";

NET "FLASH_WE_B" LOC = "M16";

NET "FMC_CLK0_M2C_N" LOC = "A10";

NET "FMC_CLK0_M2C_P" LOC = "C10";

NET "FMC_CLK1_M2C_N" LOC = "V9";

NET "FMC_CLK1_M2C_P" LOC = "T9";

NET "FMC_LA00_CC_N" LOC = "C9";

NET "FMC_LA00_CC_P" LOC = "D9";

NET "FMC_LA01_CC_N" LOC = "C11";

NET "FMC_LA01_CC_P" LOC = "D11";

NET "FMC_LA02_N" LOC = "A15";

NET "FMC_LA02_P" LOC = "C15";

NET "FMC_LA03_N" LOC = "A13";

NET "FMC_LA03_P" LOC = "C13";

NET "FMC_LA04_N" LOC = "A16";

NET "FMC_LA04_P" LOC = "B16";

NET "FMC_LA05_N" LOC = "A14";

NET "FMC_LA05_P" LOC = "B14";

NET "FMC_LA06_N" LOC = "C12";

NET "FMC_LA06_P" LOC = "D12";

NET "FMC_LA07_N" LOC = "E8";