SP601 Hardware User Guide www.xilinx.com 53

UG518 (v1.1) August 19, 2009

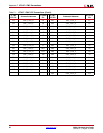

NET "FMC_LA07_P" LOC = "E7";

NET "FMC_LA08_N" LOC = "E11";

NET "FMC_LA08_P" LOC = "F11";

NET "FMC_LA09_N" LOC = "F10";

NET "FMC_LA09_P" LOC = "G11";

NET "FMC_LA10_N" LOC = "C8";

NET "FMC_LA10_P" LOC = "D8";

NET "FMC_LA11_N" LOC = "A12";

NET "FMC_LA11_P" LOC = "B12";

NET "FMC_LA12_N" LOC = "C6";

NET "FMC_LA12_P" LOC = "D6";

NET "FMC_LA13_N" LOC = "A11";

NET "FMC_LA13_P" LOC = "B11";

NET "FMC_LA14_N" LOC = "A2";

NET "FMC_LA14_P" LOC = "B2";

NET "FMC_LA15_N" LOC = "F9";

NET "FMC_LA15_P" LOC = "G9";

NET "FMC_LA16_N" LOC = "A7";

NET "FMC_LA16_P" LOC = "C7";

NET "FMC_LA17_CC_N" LOC = "T8";

NET "FMC_LA17_CC_P" LOC = "R8";

NET "FMC_LA18_CC_N" LOC = "T10";

NET "FMC_LA18_CC_P" LOC = "R10";

NET "FMC_LA19_N" LOC = "P7";

NET "FMC_LA19_P" LOC = "N6";

NET "FMC_LA20_N" LOC = "P8";

NET "FMC_LA20_P" LOC = "N7";

NET "FMC_LA21_N" LOC = "V4";

NET "FMC_LA21_P" LOC = "T4";

NET "FMC_LA22_N" LOC = "T7";

NET "FMC_LA22_P" LOC = "R7";

NET "FMC_LA23_N" LOC = "P6";

NET "FMC_LA23_P" LOC = "N5";

NET "FMC_LA24_N" LOC = "V8";

NET "FMC_LA24_P" LOC = "U8";

NET "FMC_LA25_N" LOC = "N11";

NET "FMC_LA25_P" LOC = "M11";

NET "FMC_LA26_N" LOC = "V7";

NET "FMC_LA26_P" LOC = "U7";

NET "FMC_LA27_N" LOC = "T11";

NET "FMC_LA27_P" LOC = "R11";

NET "FMC_LA28_N" LOC = "V11";

NET "FMC_LA28_P" LOC = "U11";

NET "FMC_LA29_N" LOC = "N8";

NET "FMC_LA29_P" LOC = "M8";

NET "FMC_LA30_N" LOC = "V12";

NET "FMC_LA30_P" LOC = "T12";

NET "FMC_LA31_N" LOC = "V6";

NET "FMC_LA31_P" LOC = "T6";

NET "FMC_LA32_N" LOC = "V15";

NET "FMC_LA32_P" LOC = "U15";

NET "FMC_LA33_N" LOC = "N9";

NET "FMC_LA33_P" LOC = "M10";

NET "FMC_PRSNT_M2C_L" LOC = "U13";

NET "FMC_PWR_GOOD_FLASH_RST_B" LOC = "B3";

NET "FPGA_AWAKE" LOC = "P15";

NET "FPGA_CCLK" LOC = "R15";

NET "FPGA_CMP_CLK" LOC = "U16";

NET "FPGA_CMP_CS_B" LOC = "P13";