B - 1

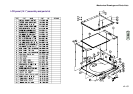

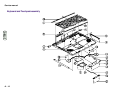

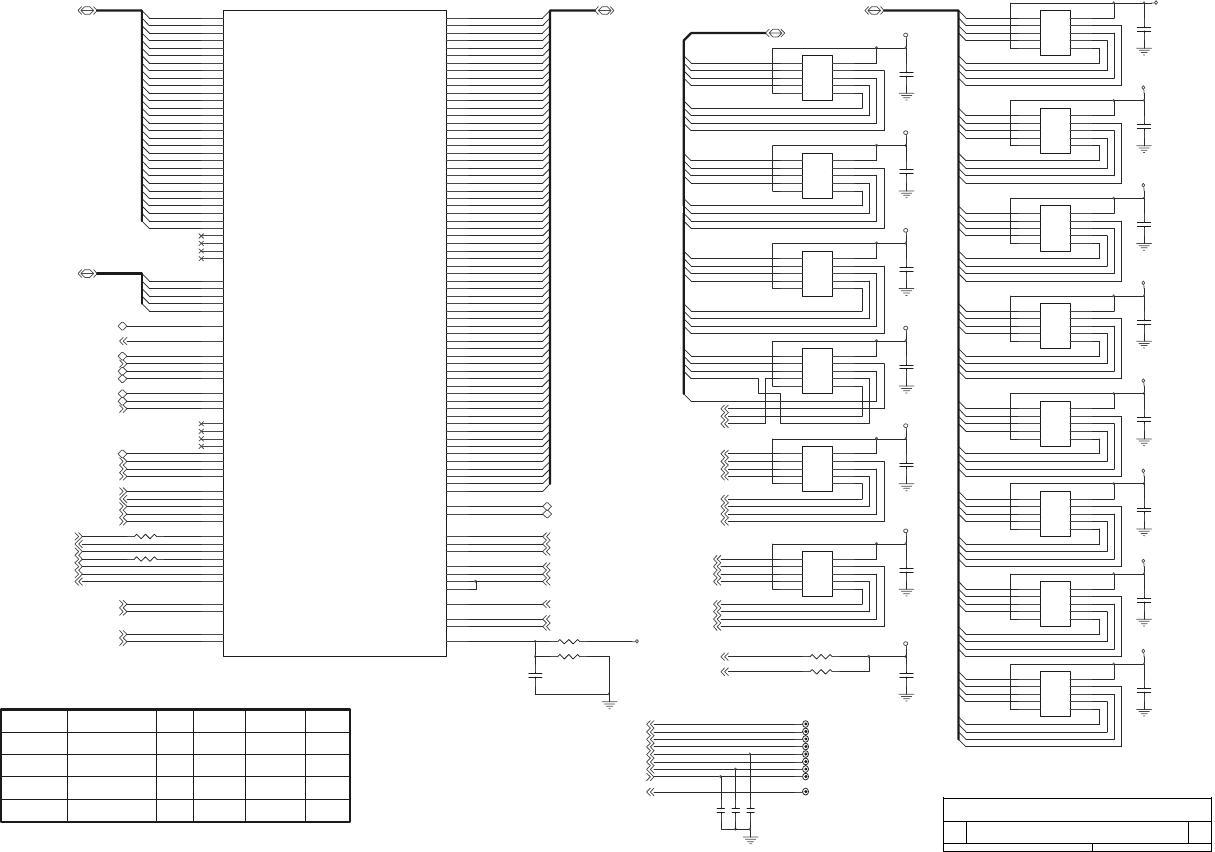

Schematic Diagrams

71-22C00-D02

A

CPU & AGTL TERMINATION

Custom

1

31

Monday, March 05, 2001

Title

Size Document Number Rev

Date : Sheet

of

ÂÅ ¤ Ñ ¹q ¸£ CLEVO CO.

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

VCCT

V_IO

FLUSH# (2)

PICD1 (2)

PICD0 (2)

CPURST# (4)

INIT# (2,10)

PCLKPIC (3)

TDO(2)

PRDY#

CP U_ FE RR #(2)

BSEL0 (2,3)

HCLKCPU (3)

BSEL1 (2,3)

CPURST#(4)

ADS#(4)

IERR#(2)

HD#[0..63](4)HD#[0..63] (4)HA#[3..31](4)

HA#[3..31] (4)

ADS#(4)

DBSY# (4)

DRDY# (4)

HI T #(4)

HITM#(4)

HT R DY #(4)

BNR#(4)

RS#0(4)

RS#1(4)

RS#2(4)

DEFER#(4)

BPRI#(4)

BREQ0#(4)

HLOCK#(4)

A20M#(2,10)

IGNNE#(2,10)

PWRGOOD(2)

SMI#(2,10)

TCK(2)

TDI(2)

TMS(2)

TRST#(2)

PREQ#(2)

INTR(2,10)

NMI(2,10)

STPCLK#(2,10)

SLP#(2,10)

PRDY#

HREQ#[0..4](4)

HREQ#4(4)

HREQ#0(4)

BREQ0#(4)

RS#2(4)

DBSY#(4)

DRDY#(4)

HI T #(4)

HT RDY #(4)

HITM#(4)

RS#1(4)

DEFER#(4)

HLOCK#(4)

HREQ#3(4)

RS#0(4)

HREQ#2(4)

BPRI#(4)

HREQ#1(4)

BNR#(4)

TDO(2)

TRST#(2)

PRDY#

TDI(2)

CPURST#(4)

PREQ#(2)

TCK(2)

TMS(2)

IT P _R ST #(26)

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

DBSY#

DRDY#

PCLKPIC

PICD1

PICD0

INIT#

FLUSH#

CPURST#

HD#[0..63]

INT R

NMI

STPCLK#

SLP#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

A20M#

CPU_ FE RR#

IGNNE #

PWRGOOD

SMI#

HT RDY #

RS#0

RS#1

RS#2

BREQ0#

BPRI#

BNR#

HLOCK#

HIT #

HITM#

DEFER#

ADS#

IERR#

BSEL0

HCLKCPU

BSEL1

HD#[0..63]

HD#1

HD#5

HD#8

HD#17

HD#0

HD#6

HD#15

HD#4

HD#2

HD#14

HD#11

HD#13

HD#10

HD#12

HD#18

HD#9

HD#35

HD#32

HD#29

HD#31

HD#26

HA#29 HD#25

HD#19

HD#33

HD#24

HD#21

HD#23

HD#16

HD#20

HA#7 HD#3

HD#7

HD#30

P R DY # H D#2 8

HD#22

HD#34

HD#43

HD#38

HD#36

HD#37

HD#39

HD#45

HD#44

HD#42

HD#27

HD#51

HD#49

HD#41

HD#47

HD#40

HD#52

HD#48

HD#59

HD#63

HD#57

HD#55

HD#46

HD#50

HD#58

HD#53

HD#54

HD#56

HD#61

HD#62

HD#60

CPURST#

ADS#

CLKREF

Z74 4

Z74 3

HA#[3..31]

HA#9

HA#26

HA#13

HA#5

HA#9

HA#30

HA#22

HA#12

HA#6

HA#[3..31]

HA#24

HA#17

HA#28

HA#10

HA#27

HA#16

HA#4

HA#21

HA#6

HA#15

HA#4

HA#19

HA#7

HA#22

HA#12

HA#27

HA#8

HA#16

HA#11

HA#29

HA#26

HA#3

HA#31

HA#25

HA#14

HA#25

HA#14

HA#17

HA#19

HA#18

HA#28

HA#10

HA#8

HA#30

HA#5

HA#20

HA#18

HA#21

HA#24

HA#3

HA#31

HA#13

HA#23

HA#20

HA#23

HA#15

BREQ0#

RS#2

DBSY#

DRDY#

HIT #

HT RDY #

HITM#

RS#1

DEFER#

HLOCK#

HREQ#1

HREQ#[0..4]

HREQ#4

HREQ#2

HREQ#4

HREQ#0

HREQ#3

HREQ#0

HREQ#3

RS#0

HREQ#2

BPRI#

HREQ#1

BNR#

HA#11

PREQ#

PRDY#

CPURST#

TRST#

TDO

TDI

TMS

TCK

IT P _RST #

C33 7

.1U

C36 7

.1U

C32 5

.1U

C28 7

.1U

C30 7

.1U

C40

.1U

C41

.1U

C42

.1U

C23 4

.1U

C36 5

.1U

C36 8

.1U

C35 7

.1U

C12 6

.1U

C36 9

.1U

C35 6

.1U

RP7

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

R30 8

56

RP6

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP4

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP5

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP1

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP2

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP3

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP11

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP17

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP9

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP8

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

R31 4

56

R300 150(1%)(0805)

R299 150(1%)(0805)

C32 2

.1U

R168 47

R167 47

CPU SUPPORT

Socket370

P3(.18)

Socket370

Celeron(.18)

VCC_Core VTT V_CMOS A(MAX) FSB

1.5V

1.5V

1.5V

1.5V

1.5V

2.5V2.0V

850:16.2A

1G:19.4A

500:14.2A

100MHz

133MHz

66MHz

Socket370

P3(.18)

500-550E:1.6V

600-850:1.65V

533-933:1.65V

1G:1.7V

RP16

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

U9A

CELEONP 3

AK8

AH12

AH8

AN9

AL15

AH10

AL9

AH6

AK10

AN5

AL7

AK14

AL5

AN7

AE1

Z6

AG3

AC3

AJ1

AE3

AB6

AB4

AF6

Y3

AA1

AK6

Z4

AA3

AD4

AK18

AH16

AH18

AL19

AL17

AN31

AE35

AN29

AN17

AH14

AK20

AL25

AL23

AN19

G3 3

E37

C35

E35

AN25

AH26

AH22

AK28

AE33

AC35

AG37

AK26

AJ35

AL33

AN37

AN35

AK32

AN33

J37

A35

M36

L37

AG35

AH30

W1

T4

N1

M6

U1

S3

T6

J1

S1

P6

Q3

M4

Q1

L1

N3

U3

H4

R4

P4

H6

L3

G1

F8

G3

K6

E3

E1

F12

A5

A3

J3

C5

F6

C1

C7

B2

C9

A9

D8

D10

C15

D14

D12

A7

A11

C11

A21

A15

A17

C13

C25

A13

D16

A23

C21

C19

C27

A19

C23

C17

A25

A27

E25

F16

AL27

AN27

J33

L35

J35

AG33

AE37

X4

W37

AJ33

X6

AC1

W3

AF4

AJ31

Y33

AH4

A#3

A#4

A#5

A#6

A#7

A#8

A#9

A#10

A#11

A#12

A#13

A#14

A#15

A#16

A#17

A#18

A#19

A#20

A#21

A#22

A#23

A#24

A#25

A#26

A#27

A#28

A#29

A#30

A#31

REQ#0

REQ#1

REQ#2

REQ#3

REQ#4

ADS#

IERR#

BR0#

BPRI#

BNR#

LOCK#

HIT #

HITM#

DEFER#

BP#2

BP#3

BPM#0

BPM#1

TRDY#

RS#0

RS#1

RS#2

A20M#

FE RR#

IGNNE #

PWGOOD

SMI#

TCK

TDO

TDI

TMS

TRST#

PREQ#

PRDY#

LINT0#/INTR

LINT1#/NMI

STPCLK#

SLP#

D#0

D#1

D#2

D#3

D#4

D#5

D#6

D#7

D#8

D#9

D#1 0

D#1 1

D#1 2

D#1 3

D#1 4

D#1 5

D#1 6

D#1 7

D#1 8

D#1 9

D#2 0

D#2 1

D#2 2

D#2 3

D#2 4

D#2 5

D#2 6

D#2 7

D#2 8

D#2 9

D#3 0

D#3 1

D#3 2

D#3 3

D#3 4

D#3 5

D#3 6

D#3 7

D#3 8

D#3 9

D#4 0

D#4 1

D#4 2

D#4 3

D#4 4

D#4 5

D#4 6

D#4 7

D#4 8

D#4 9

D#5 0

D#5 1

D#5 2

D#5 3

D#5 4

D#5 5

D#5 6

D#5 7

D#5 8

D#5 9

D#6 0

D#6 1

D#6 2

D#6 3

DBSY#

DRDY#

PICCLK

PICD1

PICD0

INIT#

FLUSH#

RES ET #

BCLK

BSEL0

A#32

A#33

A#34

A#35

BSEL1

CLKREF

RES ET #

RP14

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

RP15

TSMC8R-56

1

2

3

4

5

10

9

8

7

6

1

2

3

4

5

10

9

8

7

6

C48 0

.1U

C48 1

.1U

C48 2

.1 U(R)

TP187

TP188

TP189

TP190

TP191

TP192

TP193

TP194

TP195

71-22C00-D01

Appendix B: Schematic Diagrams