B - 3

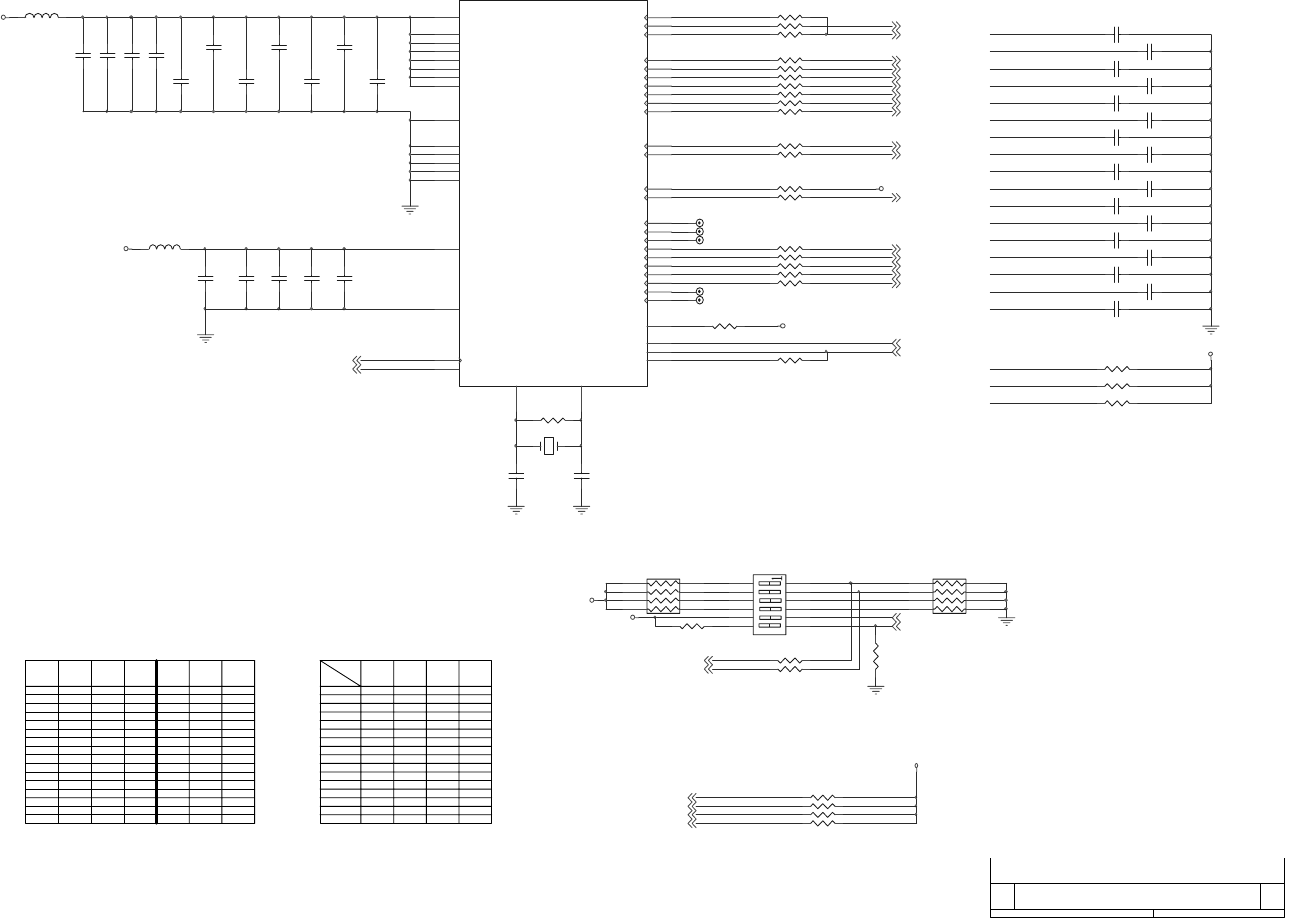

Schematic Diagrams

71-22C00-D02

2.0

CLOCK GENERATOR

Custom

331

0200-03.SCH

Monday, March 05, 2001

Title

Size Docum ent Number Rev

Da te: Sh eet

of

ÂÅ ¤Ñ ¹q ¸£ CLEVO CO.

VCC3

VCC3

VCC3

VCC3

VCC3

V_I O

VCC3

VCC3

MD44(5 ,6 )

MD43(5 ,6 )

MD42(5 ,6 )

MD41(5 ,6 )

CPUSTP# (10)

PCISTP#

MEMCLK4 (5)

MEMCLK3 (5)

MEMCLK2 (5)

MEMCLK1 (5)

DCLKREF (4)

PCLK80P (25)

AGPCLK0 (7)

HCLK630S (4)

HCLKCPU (1)

USBCLK (10)

VOSCI (7)

LPC14M (20)

PCLKSIO (21)

PCLKLPC (20)

PCLKTI (16)

SDA_ATFF(25)

SCL_ATFF(25)

BSEL0(1 ,2 )

BSEL1(1 ,2 )

PCLK630S (11)

PCLKPIC (1)

Z761

Z650

MD44

MD43

MD42

MD41

Z5 95

Z5 97

FS 3

Z5 94

Z5 96

FS 2

PCI CLK3

FS3

SDRAM7

SDRAM5

SDRAM4

PCI CLK4

REF 1

PCI CLK6

PCI CLK2

SDRAM6

C PUCL K1

FS0

FS2

C PUCL K0

SDRAM3

PCI CLK5

PCISTP#

CPUSTP#

FS1

MEMCLK 1

MEMCLK 2

SDRAM3

FS3

PCICLK5

Z3 08

CPUCLK0

SDRAM4

PCICLK4

SDRAM_STOP

PCLKPIC

MEMCLK 3SDRAM5

PCICLK2

FS2

DCLKREF

Z310

FS1

CL K2.5 V

CPUCLK1

AG PCLK0

PCICLK3

PCISTP#

Z315

SDA_ATFF

Z3 97

FS0

SDRAM7

CPUS TP #

SDRAM6

Z309

PCICLK6

Z311

Z312

HCLKCPU

HCLK630S

PCLK80P

VDDR E F

PCLKSIO

VOSCI

Z33

MEMCLK 4

SCL_ATFF

REF1

Z29

PCLKLPC

Z313

PCLK630S

LPC14M

USBCL K

PCLKTI

FS 1

FS 0

BSEL0

BSEL1

SDRAM_STOP

Z761

Z650Z8 55

R2 13

10K (R)

R2 23

10K (R)

R2 05

10K (R)

R2 22

10K (R)

RN64 8P4R_2.7K

8 1

7 2

6 3

5 4

RN60

8P4R_10K

8 1

7 2

6 3

5 4

C4 47 10P(R)

C3 90 10P(R)

C425 10P

C420 10P

C445 10P

C440 10P (R)

C398 10P (R)

C4 22 10P(R)

C393 10P

C421 10P

C426 10P

C428 10P (R)

C4 39 10P(R)

C388 10P

C385 10P

C437 10P

R3 90

10K

R3 89

10K

C442 10P

C3 97

0.01U

C3 94

.1U

C4 27

0. 01U

R3 48

33

TP172

C4 29

0.01U

C3 86

0. 01U

C4 43

4. 7U

R3 91

10K

R3 46

33

C4 38

.1U

C4 44

.1U

L56

BE AD

R3 68

33

R3 41

10

R3 40

22

Y6

14. 318MHz_DIP

1 2

L57

BE AD

TP165

C383

22P

C3 82

22P

R3 32 1 M

R3 67

33

R3 88

0

TP168

C3 96

.1U

TP173

R3 51

22

R3 81

33

C399

.1U

R3 69

22

C395

0.01U

R3 93

22

R3 52

22

C3 87

4.7U

R3 39

22

TP171

R3 50

33

R3 94

22

U26

ICS9248-135

1

48

2

3

4

5

42

7

8

9

11

12

13

10

36

22

16

26

25

30

23

24

15

20

21

33

41

40

39

38

37

19

35

34

32

31

29

28

27

44

43

45

46

47

14

17

6

18

VDDREF

REF1

FS3/REF0

GNDR E F

X1

X2

VDD

FS1/P CICLK F

FS2/P CICLK 1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

GNDPCI

VDD

GN D

GN D

FS0/48MHZ

24_48/CPU2.5_3.3V#

VDD

SDATA

SCLK

VDD

CPU_STOP#

PCI_STOP#

GN D

SDRAM_F1

SDRAM_F0

GN D

SDRAM7

SDRAM6

VDD

SDRAM5

SDRAM4

SDRAM3

SDRAM2

SDRAM1

SDRAM0

VDD

GNDL

CPUCLK2

CPUCLK1

CPUCLKF

V DDL CP U

PCICLK6

SDRAM_STOP#

VDDPCI

PD#

R3 92

22

R3 42

10

R3 47

33

C3 84

.1U

C4 41

.1U

C389

.1U

C446

.1U

R399 10K

R398 10K

R382 10K

R4 79

22(R)

R4 80

10K (R)

SW6

SW DIP-6

1

2

8

7

3

4

5

6

9

10

11

12

R5 23 1 K

R5 24

100K

1

0

0

1

1

1

1

0

1

CLOCK SELECT

1

FS1

0

0

0

1

1

1

0

1

0

FS2

0

1

0

0

1

0

0

0

0

0

1

0

1

1

1

1

1

1

FS0

0

10

1

0

0

1

0

1

0

0

1

FS3

0

1

0

1

0

0

1

0

1

1

1

1

0

0

1

0

1

1

1

CPU PCISDRAM

66

100

150

133

66.8

100

100

133

66.8

70

95

97

96.2

95

112

97

66. 8

97

95

126. 7

133

150

133. 6

133

100

100

100

100

105

129. 3

96. 2

112

33. 3

33. 3

33. 3

37. 5

33. 4

33. 3

37. 5

33. 3

33. 4

32. 3

35

31. 7

31. 7

37. 3

32. 2

32. 1 1/ 2

2/ 13

1/ 8

2/ 11

1/ 2

2/ 15

2/ 7

2/ 9

2/ 3

2/ 5

CPU RATIO SELECT

Re se r v ed

1/ 7

1/ 4

1/ 5

1/ 3

1/ 6

(NMI)

0

0

1

1

0

MD4 4

1

0

11

1

11

0

1

1

0

1

1

1

0

0

0

1

1

0

0

01

0

1

0

1

0

1

1

0

MD43

( INTR)

0

0

0

1

0

(A20M#)

0

0

1

0

1

1

0

0

1

1

MD42

0

1

1

1

1

1

1

1

0

0

0

1

0

1

0

1

0

( IGNNE#)

MD4 1

CLOSE TO CLOCK GENERATOR

CLOSE TO CLOCK GENERATOR

CLOSE T O CLOCK GENERATOR