Host Interface

4-96 C156-E227-01EN

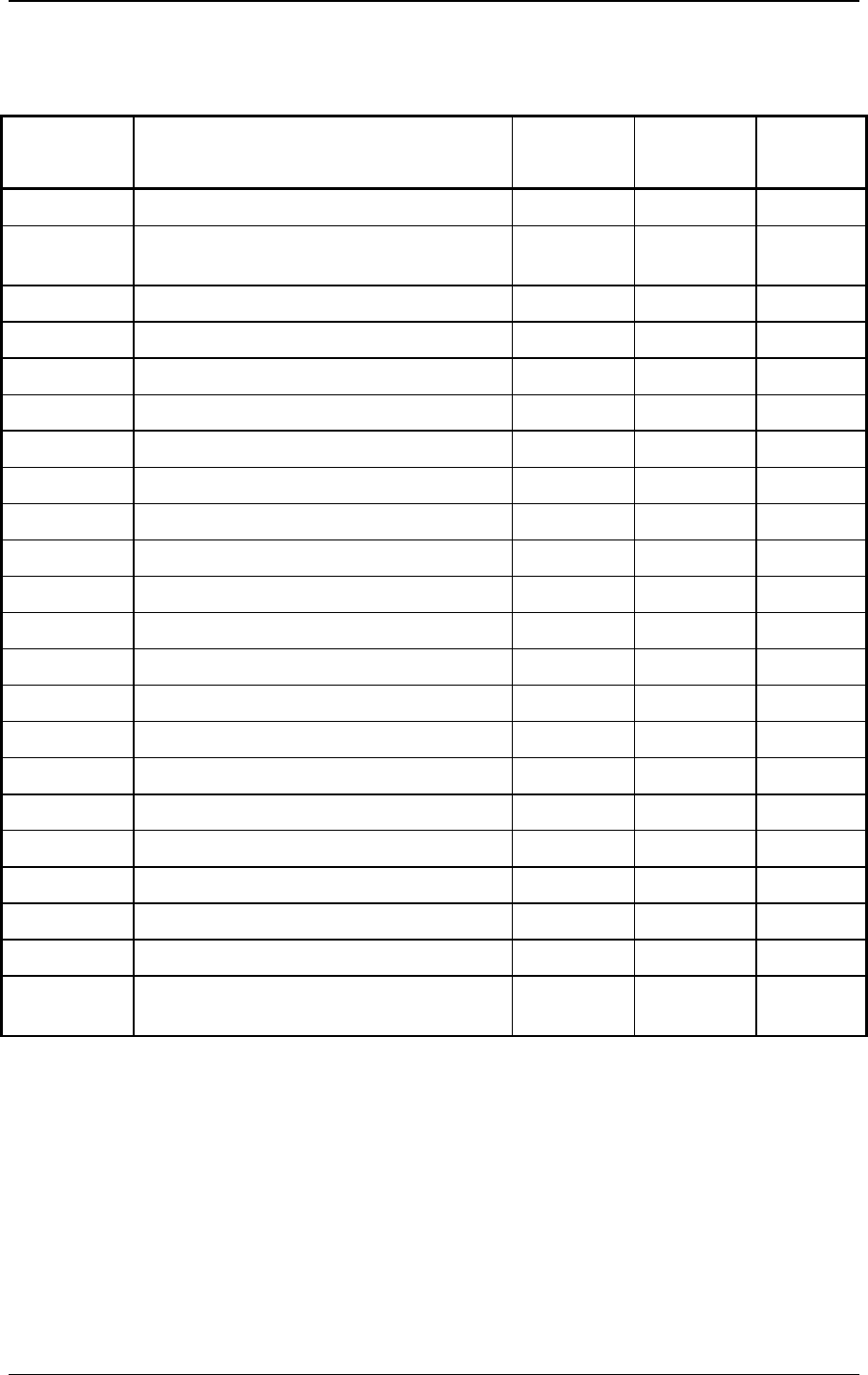

Table 4.120 Ultra DMA data out transfer parameter

Symbol Timing parameter min

(Units: ns)

max

(Units: ns)

Condition

t2CYCTYP Average 2-cycle time 120 - Mode 2

tCYC Cycle time (for non-target clock and at

clock change)

54 -

t2CYC 2-cycle time (at clock change) 115 -

tDS Data setup time on receiving side 7 -

tDH Data hold time on receiving side 5 -

tDVS Data enabled setup time on sending side 30 -

tDVH Data enabled hold time 6 -

tFS First strobe time 0 170

tLI Restricted interlock time 0 150

tMLI Minimum interlock time 20 -

tUI Non-restricted interlock time 0 -

tAZ Driver Maximum release time - 10

tZAH Output delay time 20 -

tZAD Driver Assert and negate time 0 -

tENV Envelope time 20 70

tSR STROBE to DMARDY time - 20

tRSF Ready to the last STROBE time - 60

tRP Ready to stop time 100 -

tIORDYZ Maximum IORDY release time - 20

tIORDDY STROBE operation minimum time 0 -

tACK DMACK- setup and hold time 20 -

tSS STROBE edge to DMARQ negate and

assert time

50 -