22 p5-570 Technical Overview and Introduction

POWER5 chips extensively use a fine-grained, dynamic clock-gating mechanism. This

mechanism gates off clocks to a local clock buffer if dynamic power management logic knows

that the set of latches that are driven by the buffer will not be used in the next cycle. This

allows substantial power saving with no performance impact. In every cycle, the dynamic

power management logic determines whether a local clock buffer that drives a set of latches

can be clock-gated in the next cycle.

In addition to the switching power, leakage power has become a performance limiter. To

reduce leakage power, the POWER5 chip uses transistors with low threshold voltage only in

critical paths. The POWER5 chip also has a low-power mode, enabled when the system

software instructs the hardware to execute both threads at the lowest available priority. In low

power mode, instructions dispatch once every 32 cycles at most, further reducing switching

power. The POWER5 chip uses this mode only when there is no ready task to run on either

thread.

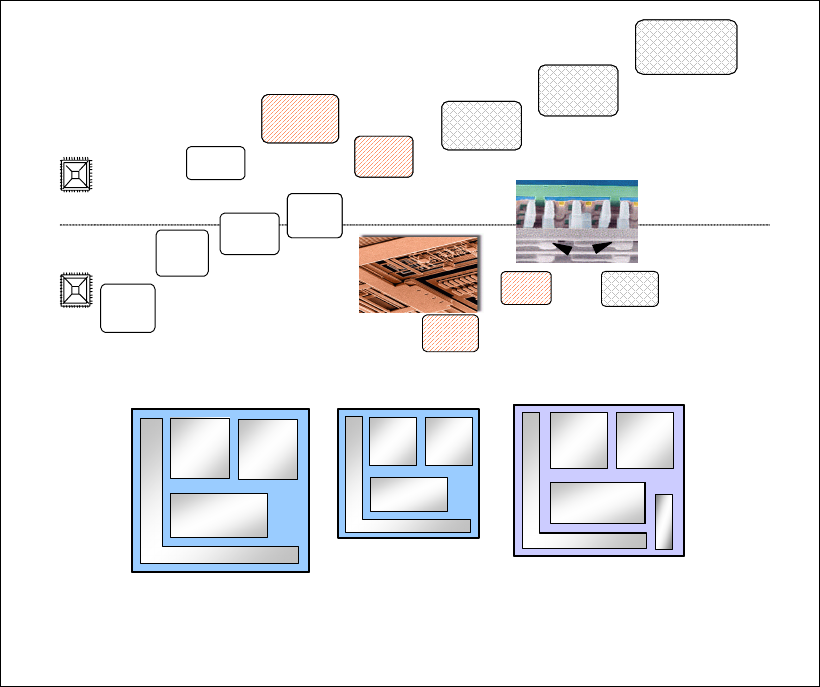

2.1.3 The POWER chip evolution

The p5-570 system complies with the RS/6000 platform architecture, which is an evolution of

the PowerPC Common Hardware Reference Platform (CHRP) specifications. Figure 2-3

shows the POWER chip evolution.

Figure 2-3 The POWER chip evolution

32bit

64bit

Note: Not all

processor speeds

available on all

models

POWER4

1.0 to 1.3

GHz

POWER4+

1.2 to 1.9 GHz

RS64-IV

600 / 750

pSeries p620, p660,

and p680

604e

332 /

375

p615, p630,

p650, p655, p670

and p690

Power3-II

333 / 375 /

450

Models 270, B80, and

POWER3 SP Nodes

RS64

125

S70

RS64-II

262.5

S7A

RS64-II

340

H70

RS64-III

450

F80, H80, M80, S80

Power3

200+

SP Nodes

+ SOI =

SOI

Copper =

F50

p630, p650, p655,

p670, and p690

1.2 to

1.9 GHz

Core

1.2 to

1.9 GHz

Core

Shared L2Shared L2

Distributed Switch

0.13 microns

2002-3

–Larger L2

–More LPARs

–High-speed Switch

POWER4+

Shared L2

Distributed Switch

0.18 microns

2001

POWER4™

–Distributed Switch

–Shared L2

–LPAR

–Autonomic computing

–Chip multiprocessing

1.0 to

1.3 GHz

Core

1.0 to

1.3 GHz

Core

Shared L2Shared L2

Distributed Switch

0.18 microns

2001

POWER4™

–Distributed Switch

–Shared L2

–LPAR

–Autonomic computing

–Chip multiprocessing

1.0 to

1.3 GHz

Core

1.0 to

1.3 GHz

Core

Shared L2

Distributed Switch

0.13 microns

2004

POWER5

TM

–Larger L2 and L3 caches

–Micro-partitioning

–Enhanced Distributed Switch

–Enhanced core parallelism

–Improved floating-point

–performance

–Faster memory environment

Mem Ctl

1.5 to

1.9 GHz

Core

1.5 to

1.9 GHz

Core

Shared L2Shared L2

Distributed Switch

0.13 microns

2004

POWER5

TM

–Larger L2 and L3 caches

–Micro-partitioning

–Enhanced Distributed Switch

–Enhanced core parallelism

–Improved floating-point

–performance

–Faster memory environment

Mem Ctl

1.5 to

1.9 GHz

Core

1.5 to

1.9 GHz

Core