42 p5-570 Technical Overview and Introduction

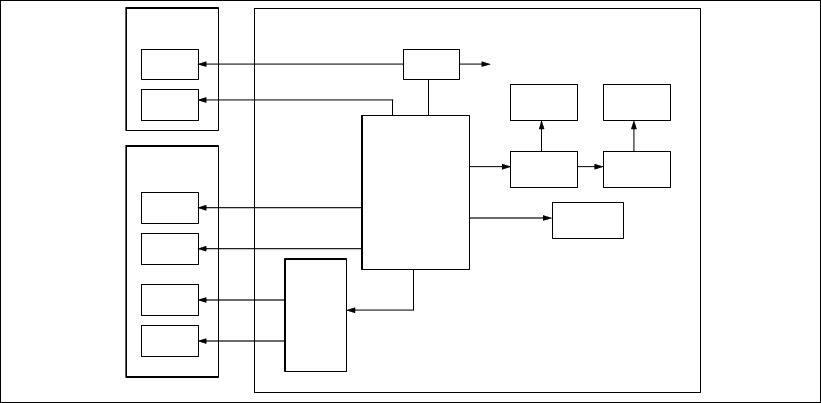

Figure 2-16 Service processor logic diagram

2.10.1 Service processor - base

The PPC405 core features a five-stage pipeline instruction processor and contains 32-bit

general purpose registers. The flash ROM contains a compressed image of a software load.

The SP base unit offers the following connections:

Two Ethernet Media Access Controller3 (MAC3) cores, which is a generic implementation

of the Ethernet Media Access (MAC) protocol compliant with ANSI/IEEE 802.3, IEEE

802.3u, ISO/IEC 8802.3 CSMA/CD Standard. The Ethernet MAC3 supports both

half-duplex (CSMA/CD) and full-duplex operation at 10/100 Mbps. Both Ethernet ports are

only visible to the service processor.

Two serial interfaces, which are accessible only though the serial ports of p5-570 on the

rear side. At the time of writing, the System Management Interface (SMI) is usable if a

connection is established to serial port 1. Terminals that are connected to serial port 2

receive only boot sequence information without manual interaction. When the HMC is

connected to the SP, the serial ports are disabled and do not provide any external

connection.

2.10.2 Service processor - extender

The SP extender unit offers the two system power control network (SPCN) ports to control the

power of the attached I/O subsystem. The SPCN control software and the service processor

software are run on the same PPC405 processor.

HMC1

HMC2

RJ45

Ethn.1

Ethn.2

RJ45

S2

S1

SPCN1

SPCN2

System planar

Rear ports

FSP

MUX

Rear ports

system

UART

#1

UART

#2

UART

#3

UART

#4

FSP-E

FSP-B

Flash

NVRAM

DDR

Interface

DDR

64 MB

ALE

SRAM

2 MB

Flash ROM

48 MB

NVRAM

controller