22 21555 PCI-to-PCI Bridge Evaluation Board User’s Guide

Optional Configurations

• In the other configuration, the central function is controlled by the intelligent subsystem

through the J1 connector.

Table 13 shows how the req# and gnt # lines must be configured for PICMG operation.

3.3 Asynchronous Clocking

Table 14 shows how to configure the J20 switches for synchronous or asynchronous operations of

the local bus. If the PICMG slot is the source of the clocks, the resistor strapping options must be

followed as described in Section 3.1. In addition, J20 SW3 must be set for asynchronous clocking

and s_clk_o needs to be disabled from the 21555.

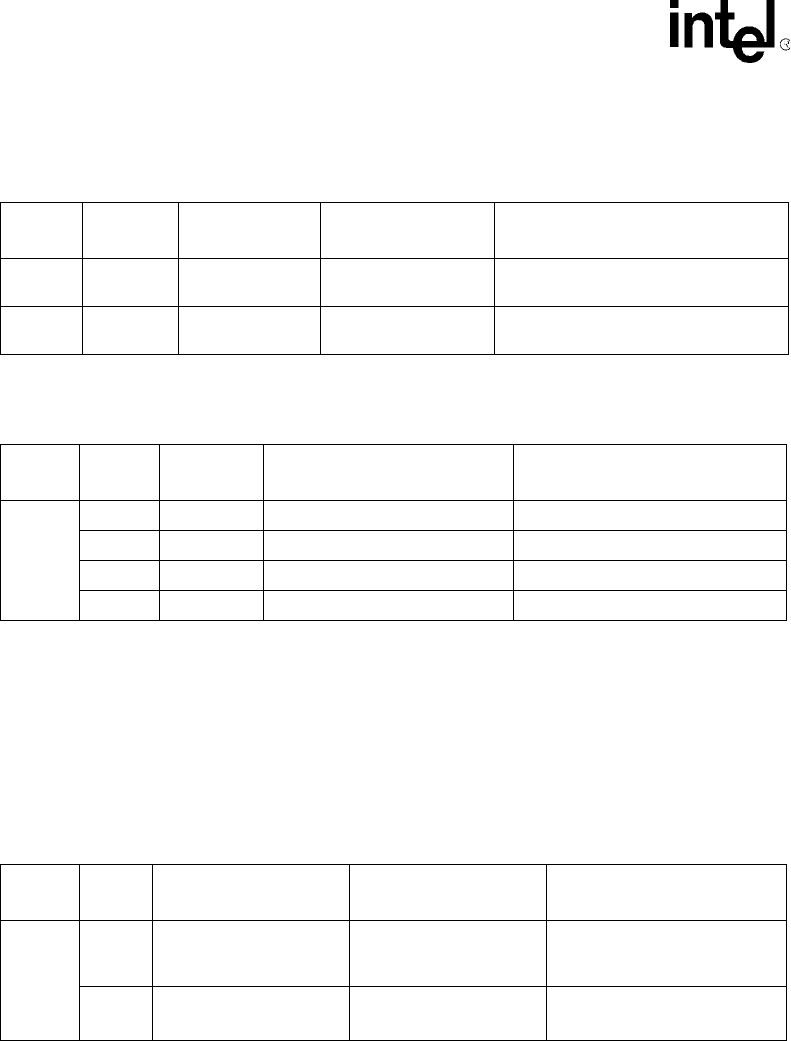

Table 12. External Arbiter Switch Option

Switch

Pack

Switch Switch Down Switch Up Description

J20 SW5

Enable the 21555

as central arbiter

System slot (J102) as

Central Function

Central Function Mode(pr_ad<6>)

J21 SW1

Disable the 21555

as central arbiter

System slot (J102) as

external arbiter.

Disable 21555 arbiter.

Table 13. J21 Switch Operations for Central Function and Arbiter Control

Switch

Pack

Switch

Request/

Grant

Switch Down

System slot (J102) as arbiter

Switch Up

21555 as arbiter

J21

SW2 req#0 PICMG GNT becomes slot grant req=req

SW3 gnt#0 PICMG REQ becomes slot grant gnt=gnt

SW4 req#1 REQ1 from PICMG slot REQ1 from drawbridge

SW5 gnt#1 GNT1 from PICMG slot GNT1 from drawbridge

Table 14. Switch Operations for Synchronous or Asynchronous Clock Control

Switch

Pack

Switch Switch Down Switch Up Description

J20

SW3

Synchronous host and

local clock domains

Asynchronous host and

local clock domains

Selects synchronous or

asynchronous operation.

(pr_ad<4>)

SW4 Disable 21555 (s_clk_o) Enable 21555 (s_clk_o)

s_clk_o

(pr_ad<5>)