PRELIMINARY 31

8XC251SA/SB/SP/SQ HIGH-PERFORMANCE CHMOS MICROCONTROLLER

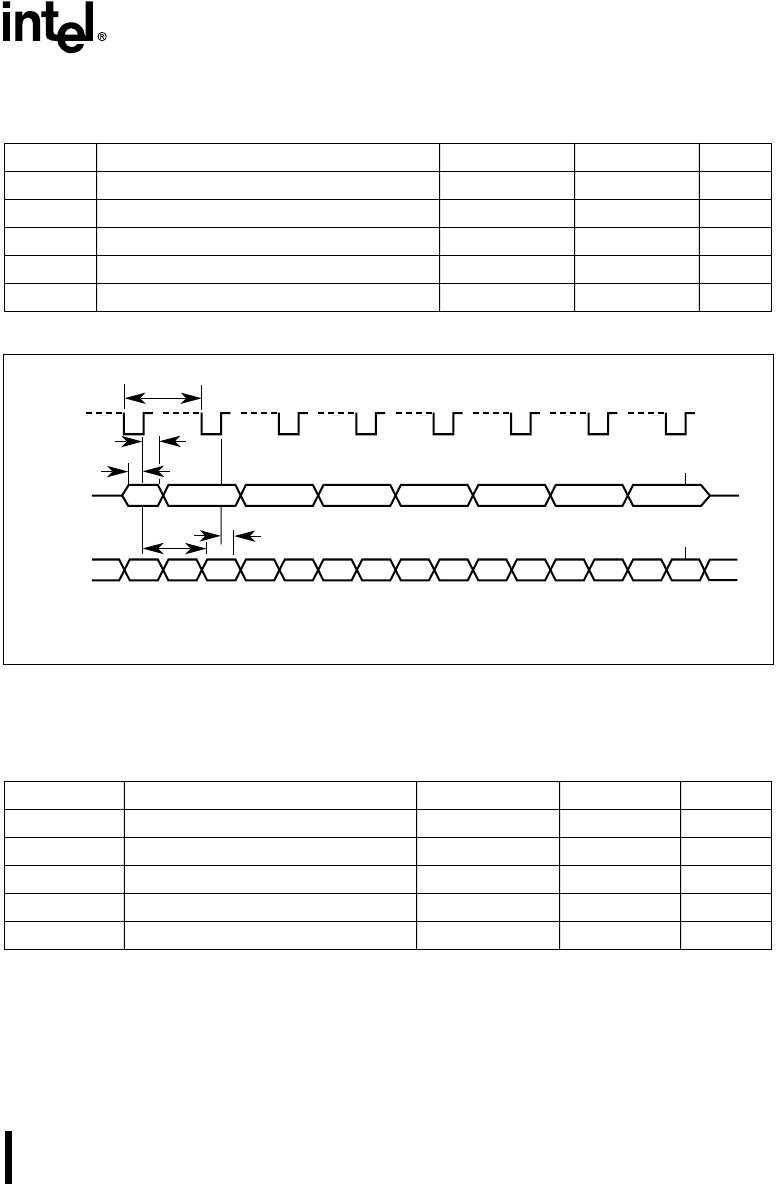

5.4 AC Characteristics — Serial Port, Shift Register Mode

Figure 17. Serial Port Waveform — Shift Register Mode

5.5 External Clock Drive

Table 14. Serial Port Timing — Shift Register Mode

Symbol Parameter Min Max Units

T

XLXL

Serial Port Clock Cycle Time 12T

OSC

ns

T

QVSH

Output Data Setup to Clock Rising Edge 10T

OSC

– 133 ns

T

XHQX

Output Data hold after Clock Rising Edge 2T

OSC

– 117 ns

T

XHDX

Input Data Hold after Clock Rising Edge 0 ns

T

XHDV

Clock Rising Edge to Input Data Valid 10T

OSC

– 133 ns

Table 15. External Clock Drive

Symbol Parameter Min Max Units

1/T

CLCL

Oscillator Frequency (F

OSC

) 16 MHz

T

CHCX

High Time 20 ns

T

CLCX

Low Time 20 ns

T

CLCH

Rise Time 10 ns

T

CHCL

Fall Time 10 ns

Valid

Valid

Valid Valid

Valid Valid

Valid

Valid

RXD

(In)

RXD

(Out)

TXD

01 2

3

4

5

6

7

T

QVXH

T

XLXL

T

XHDX

T

XHQX

T

XHDV

A2592-02

Set TI

†

Set RI

†

T

AV

†

†

TI and RI are set during S1P1 of the peripheral cycle following the shift of the eighth bit.