IA-32 Intel® Architecture Optimization

B-24

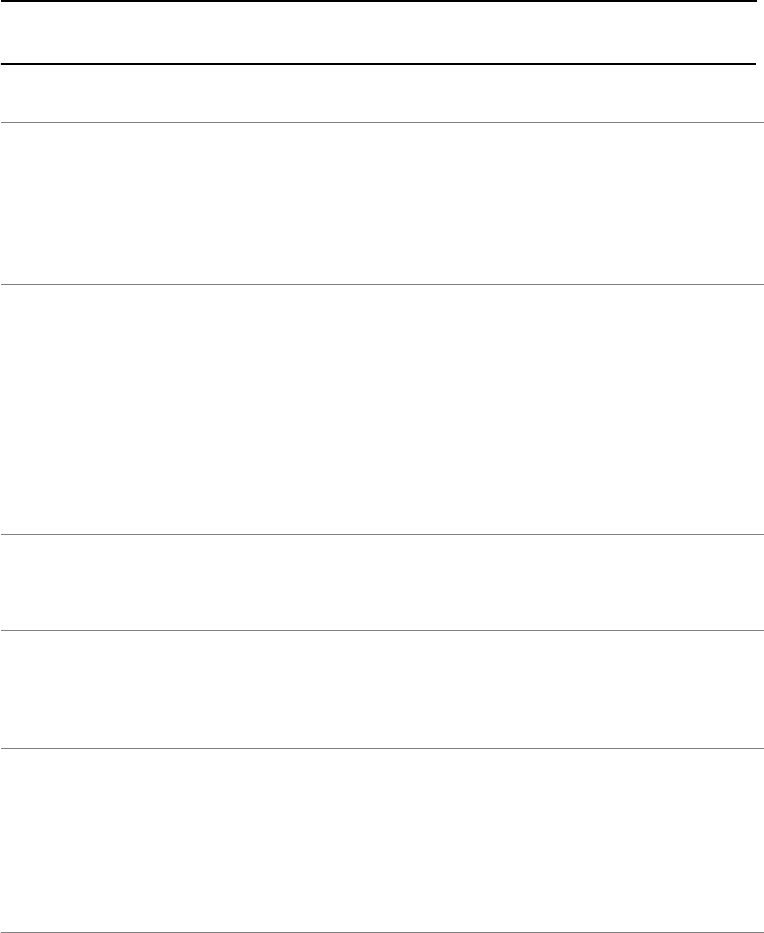

Trace Cache

Misses

The number of times

that significant

delays occurred in

order to decode

instructions and build

a trace because of a

TC miss.

BPU_fetch_request TCMISS

TC to ROM

Transfers

Twice the number of

times that the ROM

microcode is

accessed to decode

complex IA-32

instructions instead

of building|delivering

traces. (Divide the

count by 2 to get the

number of

occurrence.)

tc_ms_xfer CISC

Speculative

TC-Built Uops

The number of

speculative uops

originating when the

TC is in build mode.

uop_queue_writes FROM_TC_BUILD

Speculative

TC-Delivered

Uops

The number of

speculative uops

originating when the

TC is in deliver

mode.

uop_queue_writes FROM_TC_DELIVER

Speculative

Microcode

Uops

The number of

speculative uops

originating from the

microcode ROM (Not

all uops of an

instruction from the

microcode ROM will

be included).

uop_queue_writes FROM_ROM

continued

Table B-1 Pentium 4 Processor Performance Metrics (continued)

Metric Description

Event Name or Metric

Expression

Event Mask Value

Required