IA-32 Intel® Architecture Optimization

1-30

Data is fetched 64 bytes at a time; the instruction and data translation

lookaside buffers support 128 entries. See Table 1-3 for processor cache

parameters.

Out-of-Order Core

The processor core dynamically executes µops independent of program

order. The core is designed to facilitate parallel execution by employing

many buffers, issue ports, and parallel execution units.

The out-of-order core buffers µops in a Reservation Station (RS) until

their operands are ready and resources are available. Each cycle, the

core may dispatch up to five µops through the issue ports.

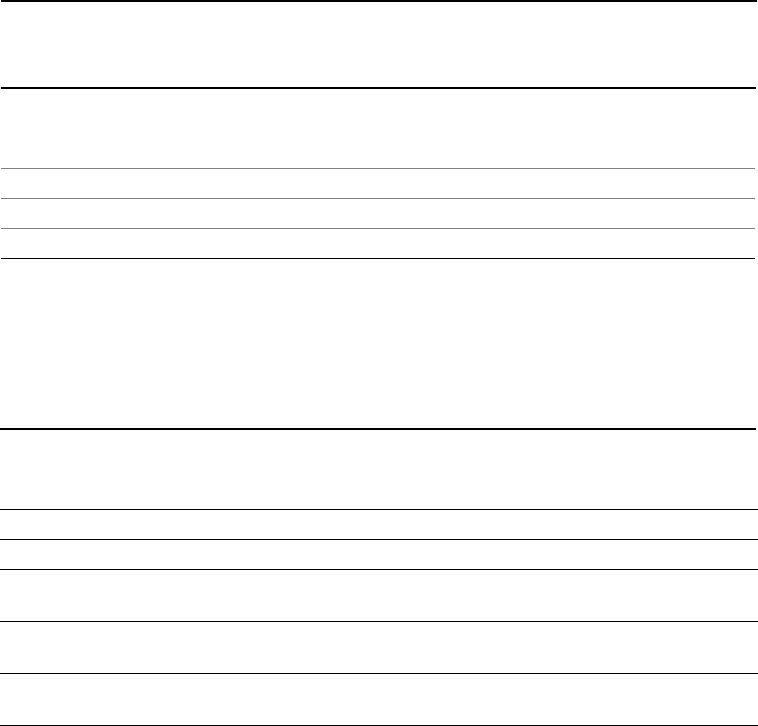

Table 1-2 Trigger Threshold and CPUID Signatures for IA-32 Processor

Families

Trigger Thresh-

old Distance

(Bytes)

Extended

Model ID

Extended

Family ID Family ID Model ID

512 0 0 15 3, 4, 6

256 0 0 15 0, 1, 2

256 0069, 13, 14

Table 1-3 Cache Parameters of Pentium M, Intel

®

Core™ Solo and

Intel

®

Core™ Duo Processors

Level Capacity

Associativity

(ways)

Line

Size

(bytes)

Access

Latency

(clocks)

Write Update

Policy

First 32 KB 8 64 3 Writeback

Instruction 32 KB 8 N/A N/A N/A

Second

(model 9)

1 MB 8 64 9 Writeback

Second

(model 13)

2 MB 8 64 10 Writeback

Second

(model 14)

2 MB 8 64 14 Writeback