DDR3THIN-MN-XXX 29 Doc. Rev. 1.11

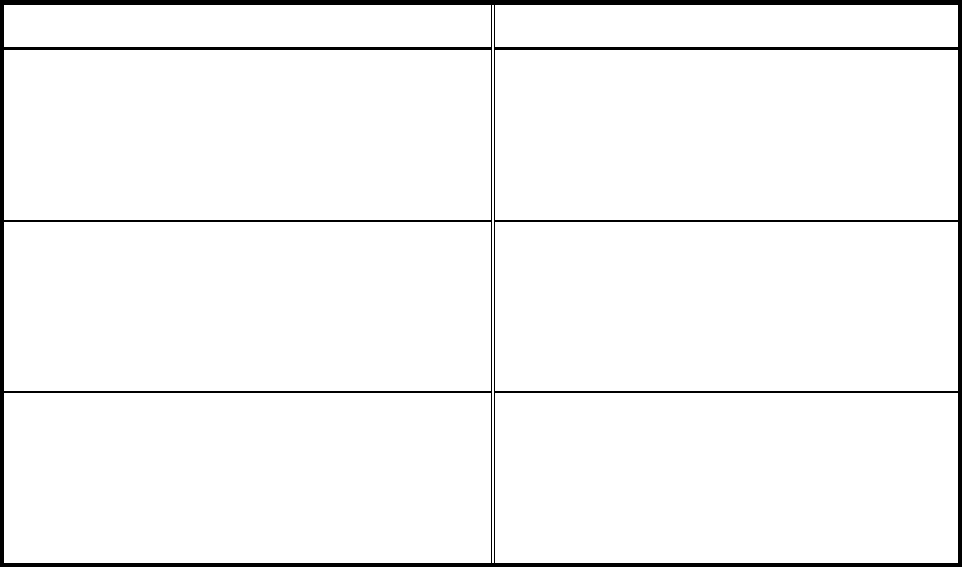

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

Group

Name

Signal

Name

DDR3

Pin #

TLA

Input

RdAChkBits

RD_A_CB7 165 M_A1:5 WrAChkBits

4

WR_A_CB7 165 M_D1:5

(OFF) RD_A_CB6 164 M_A1:4 (OFF) WR_A_CB6 164 M_D1:4

RD_A_CB5 159 M_A1:0 WR_A_CB5 159 M_D1:0

RD_A_CB4 158 M_A0:7 WR_A_CB4 158 M_D0:7

RD_A_CB3 46 M_A1:6 WR_A_CB3 46 M_D1:6

RD_A_CB2 45 M_A1:3 WR_A_CB2 45 M_D1:3

RD_A_CB1 40 M_CK1 WR_A_CB1 40 M_Q0

RD_A_CB0 39 M_A0:5 WR_A_CB0 39 M_D0:5

RdBChkBits

4

RD_B_CB7 165 M_A1:5^1 WrBChkBits

4

WR_B_CB7 165 M_D1:5^1

(OFF) RD_B_CB6 164 M_A1:4^1 (OFF) WR_B_CB6 164 M_D1:4^1

RD_B_CB5 159 M_A1:0^1 WR_B_CB5 159 M_D1:0^1

RD_B_CB4 158 M_A0:7^1 WR_B_CB4 158 M_D0:7^1

RD_B_CB3 46 M_A1:6^1 WR_B_CB3 46 M_D1:6^1

RD_B_CB2 45 M_A1:3^1 WR_B_CB2 45 M_D1:3^1

RD_B_CB1 40 M_CK1^1 WR_B_CB1 40 M_Q0^1

RD_B_CB0 39 M_A0:5^1 WR_B_CB0 39 M_D0:5^1

ADatMsks A_DM7/DQS16 230 S_A2:4 BDatMsks

4

B_DM7/DQS16 230 S_A2:4^1

(BIN) A_DM6/DQS15 221 S_A3:6 (BIN) B_DM6/DQS15 221 S_A3:6^1

A_DM5/DQS14 212 S_A1:0 B_DM5/DQS14 212 S_A1:0^1

A_DM4/DQS13 203 M_C2:0 B_DM4/DQS13 203 M_C2:0^1

A_DM3/DQS12 152 M_A0:2 B_DM3/DQS12 152 M_A0:2^1

A_DM2/DQS11 143 S_CK3 B_DM2/DQS11 143 S_CK3^1

A_DM1/DQS10 134 S_E3:5 B_DM1/DQS10 134 S_E3:5^1

A_DM0/DQS9 125 S_E2:6 B_DM0/DQS9 125 S_E2:6^1

Table 2 – B_DDR3D_2G (<=1066MT/s Read and Write) TLA Channel Grouping (cont’d.)

Notes:

1. ‘ # ‘ denotes a low-true signal

2. The ‘S’ in front of a TLA channel denotes the Slave card of the merged set

3. The ‘M’ in front of a TLA channel denotes the Master card of the merged set

4. All signals on this page are stored in the TLA7BB4’s Prime memory and will not have a

MagniVu display value