DDR3THIN-MN-XXX 59 Doc. Rev. 1.11

Figure 11 - Measuring B_DDR3D_XX WrA_DatHi / Lo Write Data Setup & Hold

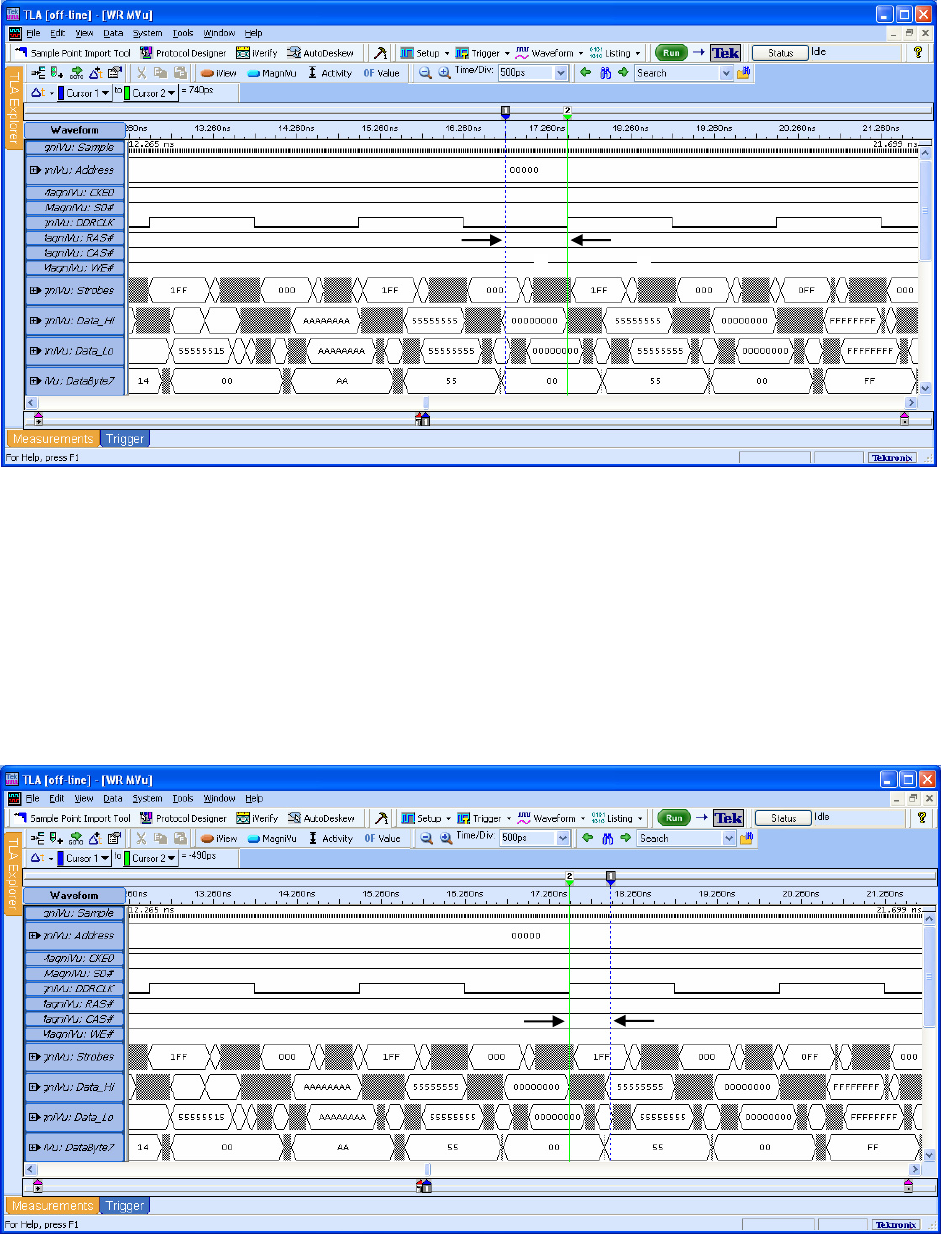

Now the sample point for the WrB_DatHi and WrB_DatLo groups must be determined (see

Figure 12). The next valid Write data (after the cycle measured above) occurs approximately

500ps after the rising edge of DDRCK0, so a suitable Setup & Hold value for the WrB_DatHi

capture group would be -508ps/742ps. As with the A data the Data_Lo group is somewhat later

than the Data_Hi group. The Data_Lo valid time starts at approximately -800ps so a suitable

Setup & Hold value for the WrB_DatLo capture group would be -801ps/1.035ns.

Figure 12 - Measuring B_DDR3D_XX WrB_DatHi / Lo Write Data Setup & Hold

The sample point positions must now be set for the WrA_DatHi, WrA_DatLo, WrB_DatHi,

WrB_DatLo groups in the Setup window (Figure 13). Note that if the Upper Strobes are being

A

B