2-143

2 Instructions

CP1E CPU Unit Instructions Reference Manual(W483)

Data Shift Instructions

2

NASL/NSLL

Sample program

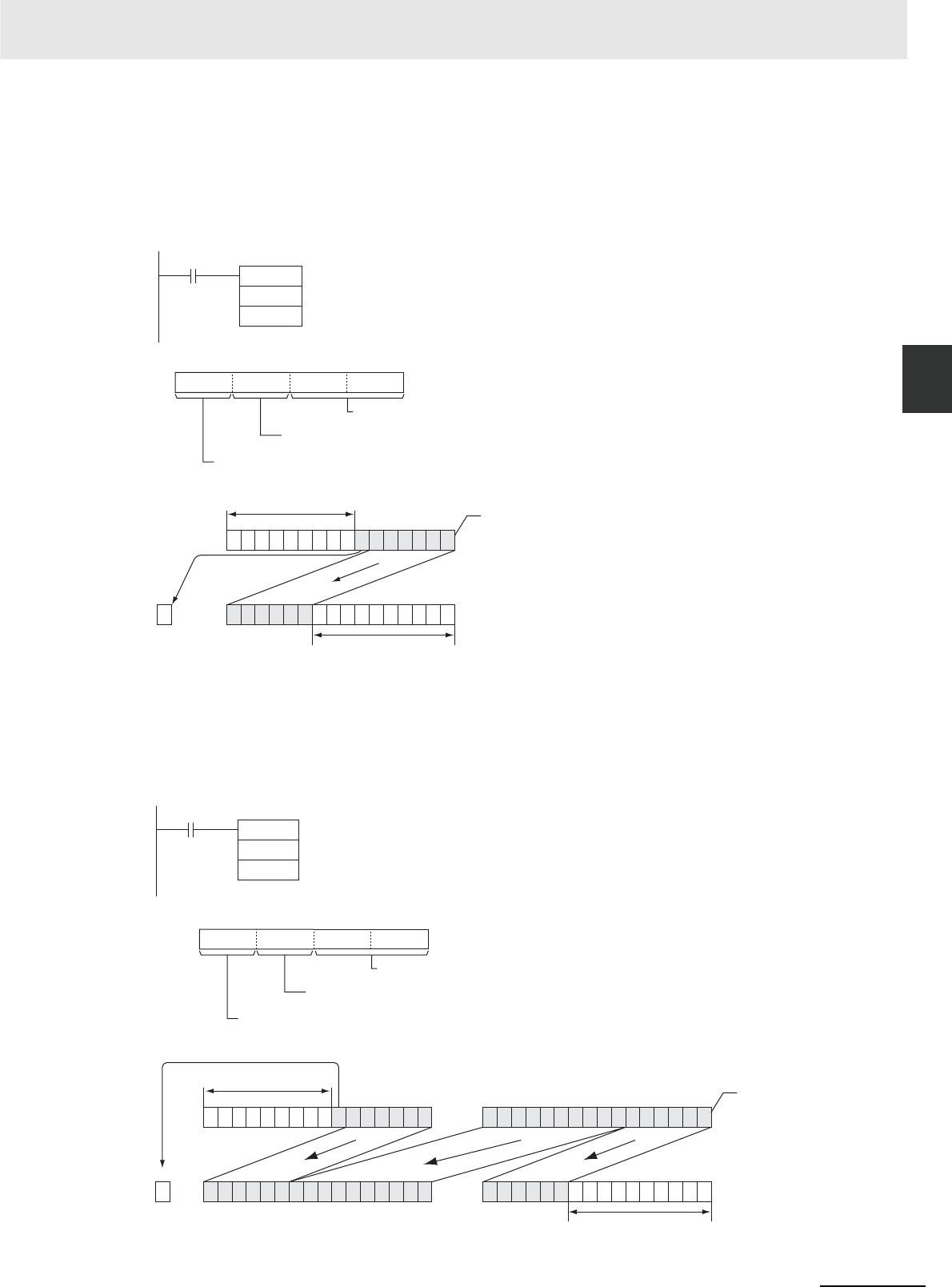

When CIO 0.00 is ON, The contents of CIO 100 is shifted 10 bits to the left (from the rightmost bit to the

leftmost bit). The number of bits to shift is specified in bits 0 to 7 of word W0 (control data). The con-

tents of bit 0 of CIO 100 is copied into bits from which data was shifted and the contents of the right-

most bit which was shifted out of range is shifted into the Carry Flag (CY). All other data is lost.

When CIO 0.00 is ON, CIO 100 and CIO 101 will be shifted to the left (from the rightmost bit to the left-

most bit) by 10 bits. The number of bits to shift is specified in bits 0 to 7 of W0 (control data). The con-

tents of bit 0 of CIO 100 is copied into bits from which data was shifted and the contents of the

rightmost bit which was shifted out of range is shifted into the Carry Flag (CY). All other data is lost.

NASL

100

W0

D

C

0.00

C0

811

8

1215

0743

0 A

No. of bits to shift: 10 bits (0A Hex)

Always 0.

Data shifted into register

8 Hex: Contents of right-most bit shifted in

015

100

5876

0151413 12 1011 4 398 21

100 1 1 1 1 1 1 1 111

CY

1

1001001

001001

Rightmost bit

Lost

No. of bits to shift: 10 bits

(Contents of the rightmost

bit is inserted.)

NSLL

100

W0

0.00

D

C

C0

811

8

1215

0743

0 A

No. of bits to shift: 10 bits (0A Hex)

Always 0.

Data shifted into register

8 Hex: Contents of right-most bit shifted in

015

101 11 0 01001

001001

87 015 8765

015

987

101 10010010 1

0

CY

1

100 1001001

001001

015 10 798

100 1

1 1 1 1 1 1 111

100100100

Rightmost bit a

Lost

No. of bits to shift: 10 bits

(Contents of the rightmost

bit is shifted in)