2-35

2 Instructions

CP1E CPU Unit Instructions Reference Manual(W483)

Sequence Control Instructions

2

Sequence Control Instructions

Overview of Interlock Instructions

Interlock Instructions

The following instruction combinations can be used to interlock outputs in a program section.

• INTERLOCK and INTERLOCK CLEAR (IL(002) and IL(003))

• MULTI-INTERLOCK DIFFERENTIATION HOLD and MULTI-INTERLOCK CLEAR (MILH(517)

and MILC(519))*

Note MILH(517) holds the status of the Differentiation Flag, so differentiated instructions that were interlocked are

executed after the interlock is cleared.

• MULTI-INTERLOCK DIFFERENTIATION RELEASE and MULTI-INTERLOCK CLEAR (MILR(518)

and MILC(519))*

Note MILR(518) does not hold the status of the Differentiation Flag, so differentiated instructions that were inter-

locked are not executed after the interlock is cleared.

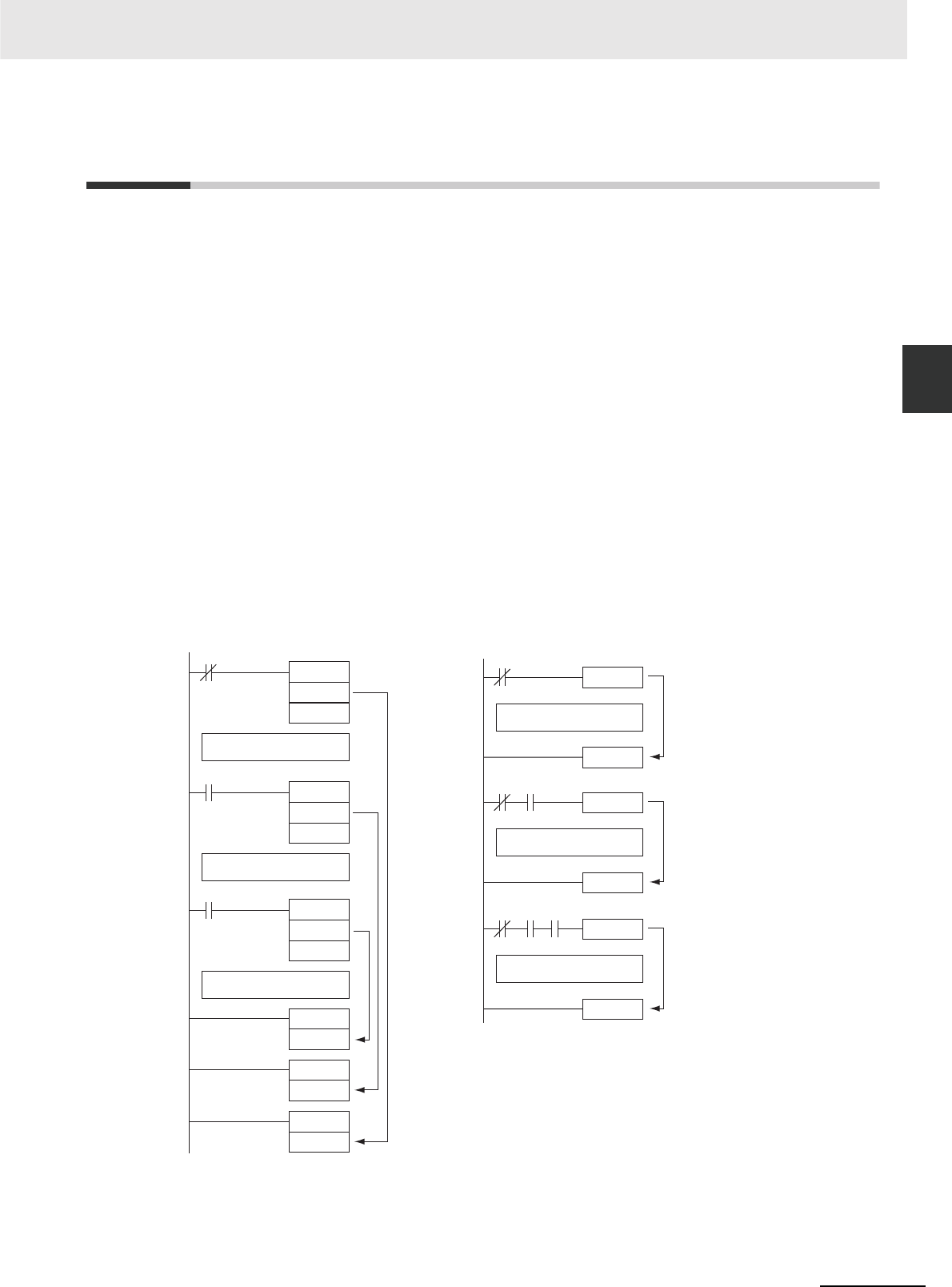

Differences between Interlocks and Multiple Interlocks

Regular interlocks (IL(002) and IL(003)) cannot be nested, but multiple interlocks (MILH(517),

MILR(518), and MILC(519)) can be nested. Ladder programming can be simplified by nesting multiple

interlocks, as shown in the following diagram.

a

MILH

0

A1

b

MILH

1

A2

c

MILH

2

A3

MILC

2

MILC

1

MILC

0

a

IL

A1

ILC

a

IL

A2

b

bc

ILC

a

IL

A3

ILC

Interlocks with MILH and MILC Interlocks with IL and ILC