Rev.1.02 Jul 01, 2005 page 167 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

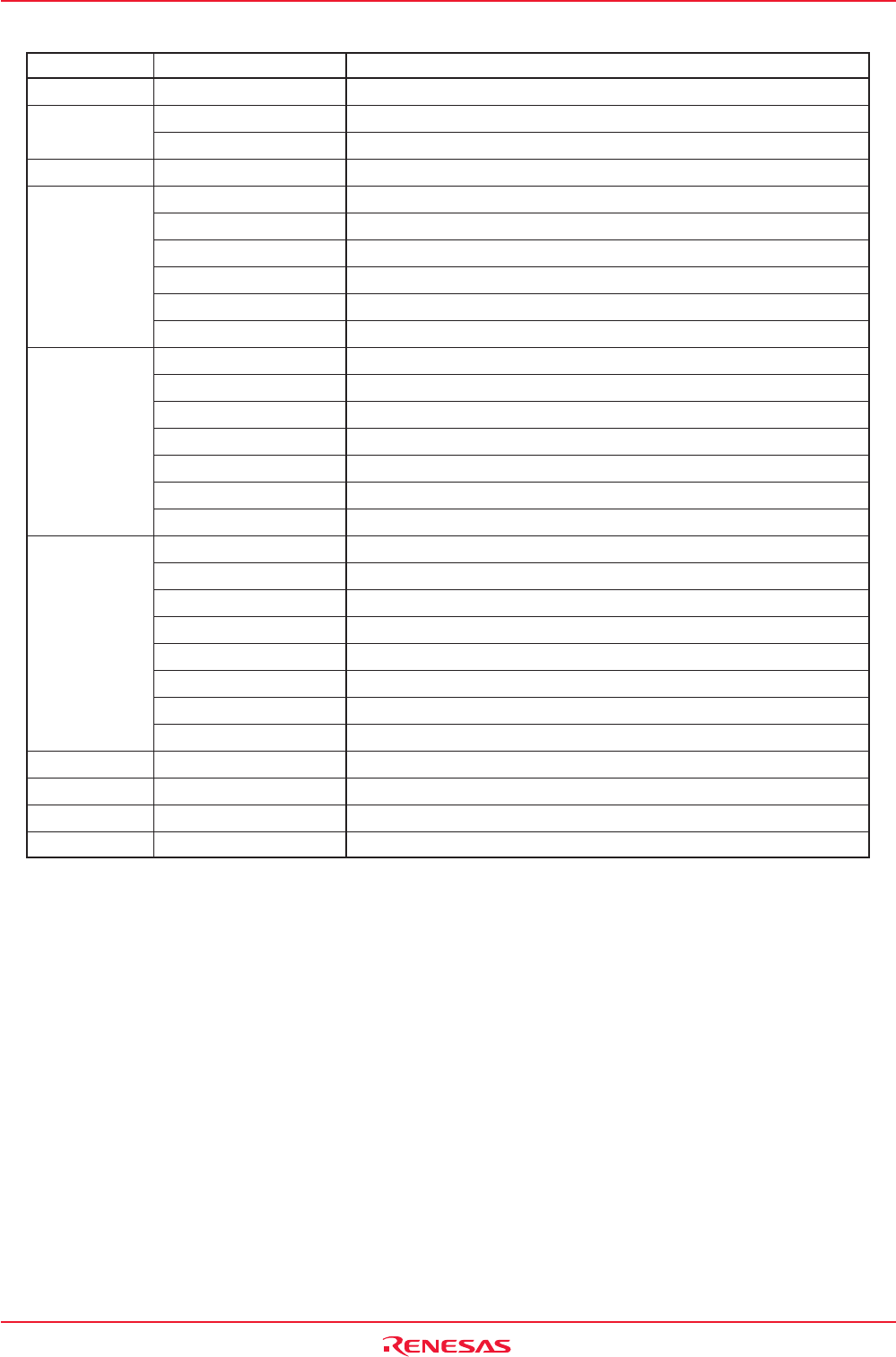

Table 14.18 Registers to Be Used and Settings in SIM Mode

Register Bit Function

U2TB

(1)

0 to 7 Set transmission data

U2RB

(1)

0 to 7 Reception data can be read

OER,FER,PER,SUM Error flag

U2BRG 0 to 7 Set a transfer rate

U2MR SMD2 to SMD0 Set to “101b”

CKDIR Select the internal clock or external clock

STPS Set to “0”

PRY Set this bit to “1” for direct format or “0” for inverse format

PRYE Set to “1”

IOPOL Set to “0”

U2C0 CLK1, CLK0 Select the count source for the U2BRG register

CRS Invalid because the CRD bit = 1

TXEPT Transmit register empty flag

CRD Set to “1”

NCH Set to “0”

CKPOL Set to “0”

UFORM Set this bit to “0” for direct format or “1” for inverse format

U2C1 TE Set this bit to “1” to enable transmission

TI Transmit buffer empty flag

RE Set this bit to “1” to enable reception

RI Reception complete flag

U2IRS Set to “1”

U2RRM Set to “0”

U2LCH Set this bit to “0” for direct format or “1” for inverse format

U2ERE Set to “1”

U2SMR

(1)

0 to 3 Set to “0”

U2SMR2 0 to 7 Set to “0”

U2SMR3 0 to 7 Set to “0”

U2SMR4 0 to 7 Set to “0”

NOTE:

1. Not all register bits are described above. Set those bits to “0” when writing to the registers in SIM mode.