Rev.1.02 Jul 01, 2005 page 205 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 18. CAN Module

Under development

This document is under development and its contents are subject to change.

-

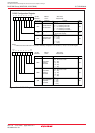

(b4-b0)

-

(b5)

-

(b6)

-

(b7)

CAN1 Control Register

(1)

C1CTLR

X0000001b

0230h

b7 b6 b5 b4 b3 b2 b1 b0

NOTE:

1. Make sure "0020h" is set to this register (addresses 0230h, 0231h). Moreover, make sure the CCLKR register is set after setting

"0020h" to this register.

RW

RW

RW

-

Set to "0"

Set to "1"

Nothing is assigned. When write, set to "0".

When read, its content is indeterminate.

0100000

Reserved Bit

Reserved Bit

Reserved Bit

Set to "0"

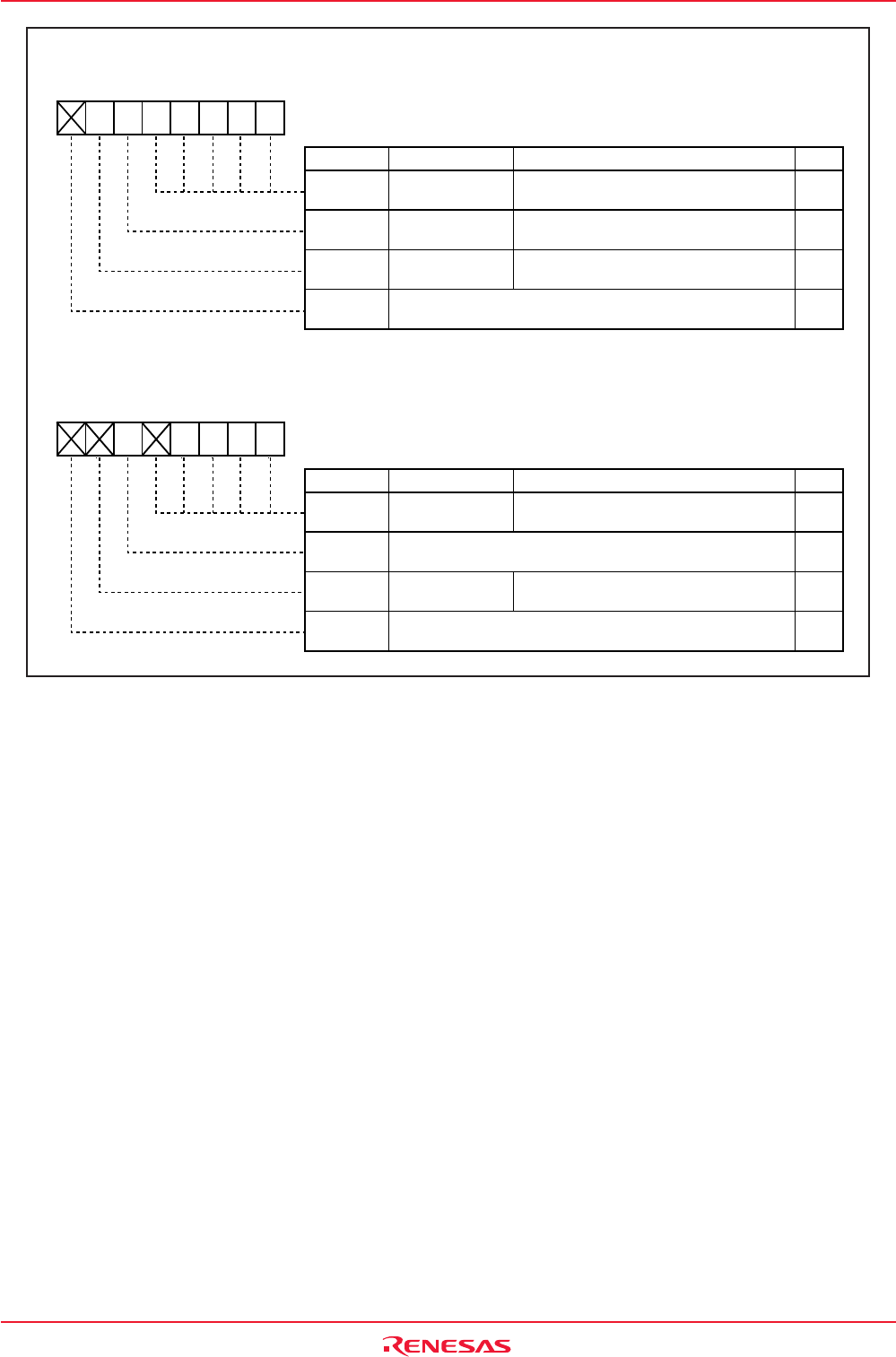

(b15) (b8)

b7 b6 b5 b4 b3 b2 b1 b0

0 0000

-

(b3-b0)

-

(b4)

-

(b5)

-

(b7-b6)

RW

-

RW

-

Set to "0"

Nothing is assigned. When write, set to "0".

When read, their contents are indeterminate.

Nothing is assigned. When write, set to "0".

When read, its content is indeterminate.

Reserved Bit

Reserved Bit

Set to "0"

Symbol

Address After Reset

C1CTLR

XX0X0000b

0231h

Symbol

Address After Reset

RWFunctionBit Symbol Bit Name

RWFunctionBit Symbol Bit Name

Figure 18.8 C1CTLR Register