Rev.1.02 Jul 01, 2005 page 171 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 14. Serial I/O

Under development

This document is under development and its contents are subject to change.

14.2 SI/Oi (i = 3 to 6)

(1)

SI/Oi is exclusive clock-synchronous serial I/Os.

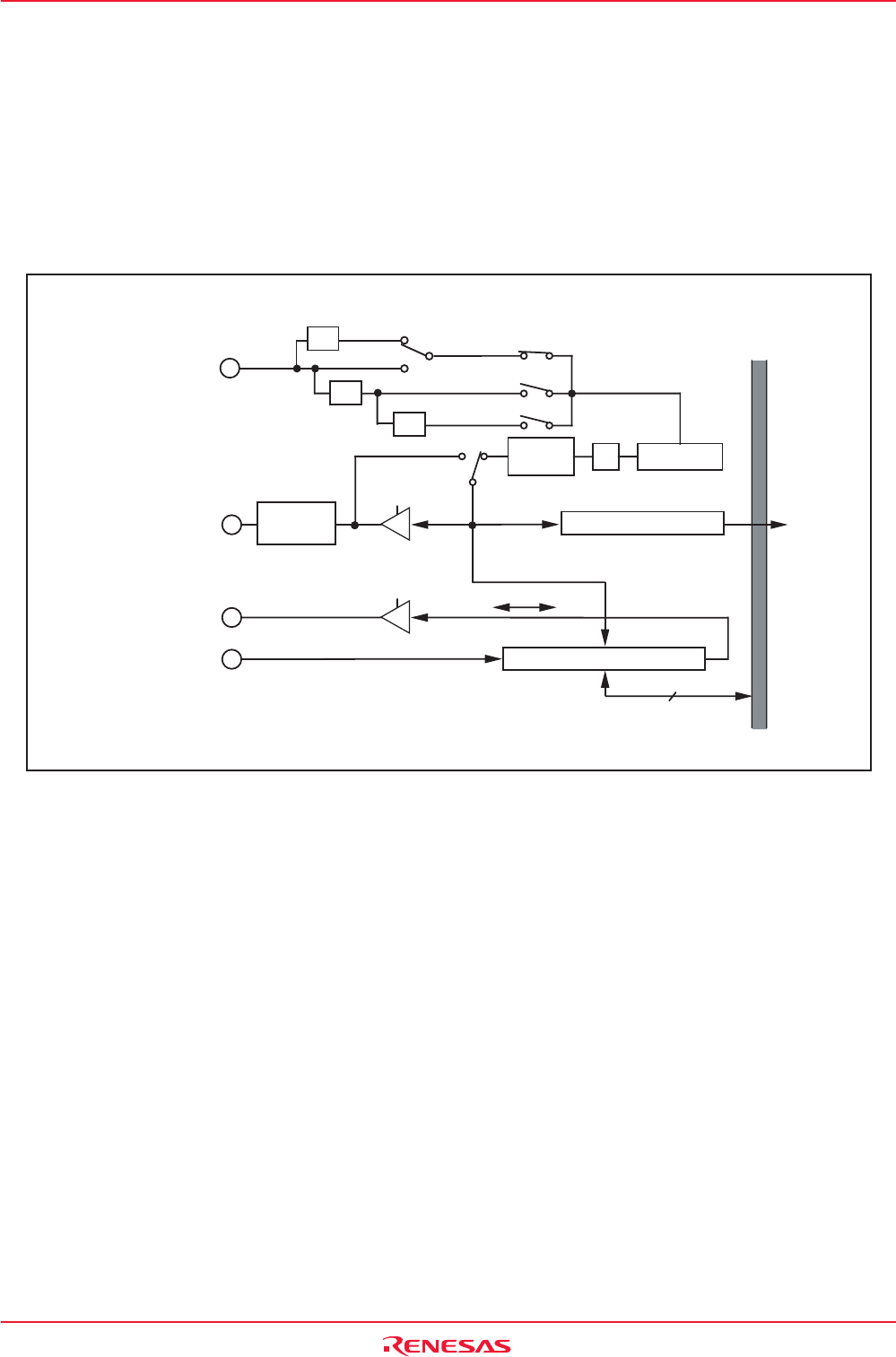

Figure 14.36 shows the block diagram of SI/Oi, and Figures 14.37 and 14.38 show the SI/Oi-related

registers.Table 14.19 lists the specifications of SI/Oi.

NOTE:

1. 100-pin version supports SI/O3 and SI/O4.

128-pin version supports SI/O3, SI/O4, SI/O5 and SI/O6.

Figure 14.36 SI/Oi Block Diagram

SiTRR register

SI/O counter i

Synchronous

circuit

Data bus

8

SI/Oi

interrupt

request

SMi5 LSB MSB

SMi2

SMi3

SMi3

SMi6

SMi1 to SMi0

SiBRG register

SMi6

i = 3 to 6 (5 and 6 are only in the 128-pin version.)

n = A value set in the SiBRG register.

1/(n+1)

1/2

CLK polarity

reversing

circuit

1/2

f1SIO

1/8

1/4

f8SIO

f32SIO

f2SIO

PCLK1=0

PCLK1=1

SMi4

Clock source select

00b

01b

10b

CLKi

SOUTi

SINi

Main clock,

PLL clock,

or on-chip oscillator clock