Rev.1.02 Jul 01, 2005 page 77 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 10. Watchdog Timer

Under development

This document is under development and its contents are subject to change.

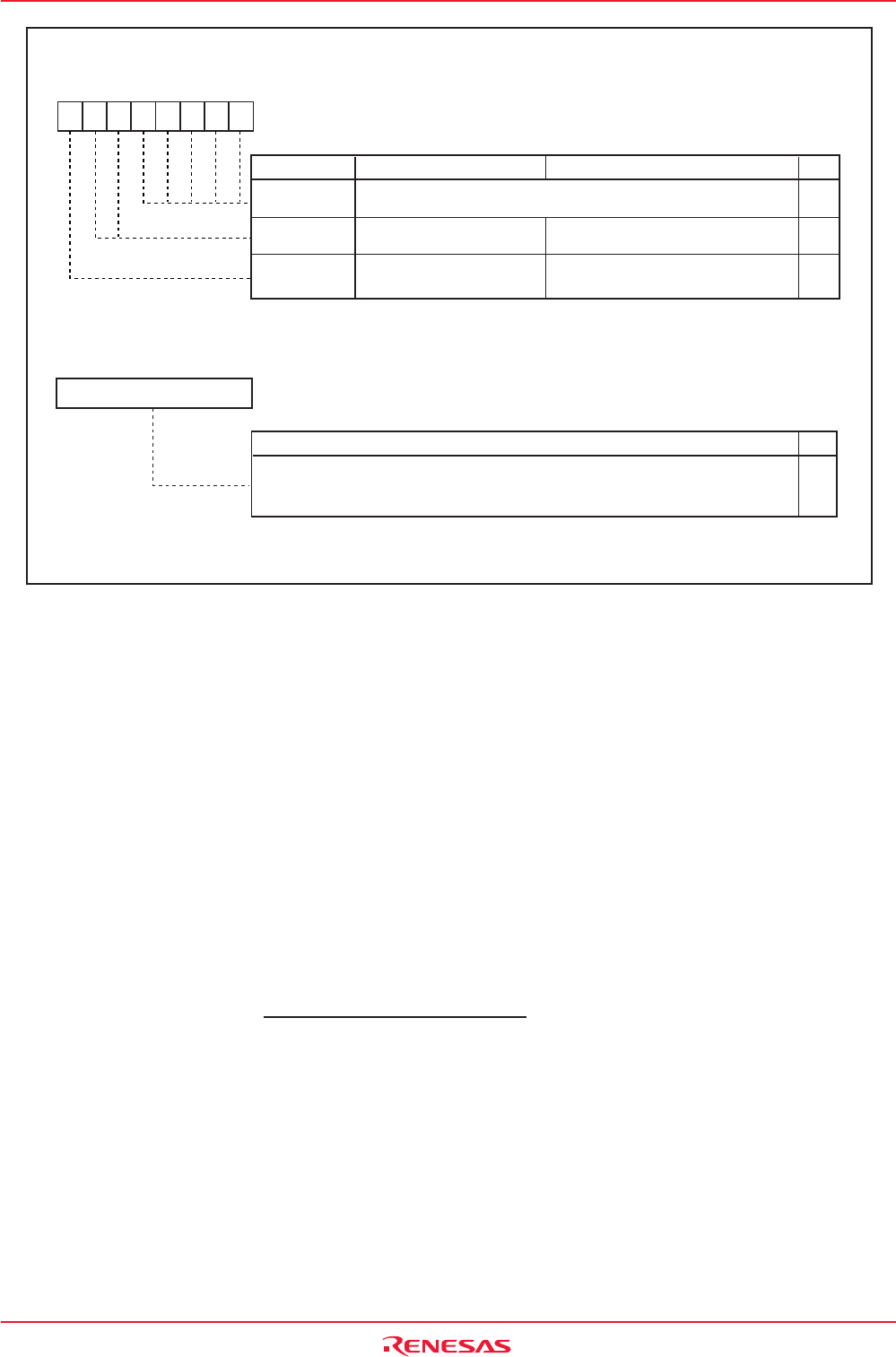

Figure 10.2 WDC Register and WDTS Register

10.1 Count Source Protective Mode

In this mode, a on-chip oscillator clock is used for the watchdog timer count source. The watchdog timer

can be kept being clocked even when CPU clock stops as a result of runaway.

Before this mode can be used, the following register settings are required:

(1) Set the PRC1 bit in the PRCR register to “1” (enable writes to the PM1 and PM2 registers).

(2) Set the PM12 bit in the PM1 register to “1” (reset when the watchdog timer underflows).

(3) Set the PM22 bit in the PM2 register to “1” (on-chip oscillator clock used for the watchdog timer count source).

(4) Set the PRC1 bit in the PRCR register to “0” (disable writes to the PM1 and PM2 registers).

(5) Write to the WDTS register (watchdog timer starts counting).

Setting the PM22 bit to “1” results in the following conditions:

• The on-chip oscillator starts oscillating, and the on-chip oscillator clock becomes the watchdog timer

count source.

• The CM10 bit in the CM1 register is disabled against write. (Writing a “1” has no effect, nor is stop mode entered.)

• The watchdog timer does not stop when in wait mode or hold state.

High-order Bit of Watchdog Timer

Prescaler Select Bit

0 : Divided by 16

1 : Divided by 128

Reserved Bit Set to "0"

WDC7

Watchdog Timer Control Register

b7 b6 b5 b4 b3 b2 b1 b0

00

RW

RO

RW

RW

-

(b4-b0)

-

(b6-b5)

FunctionBit Symbol

Bit Name

Symbol Address After Reset

WDC 000Fh 00XXXXXXb

The watchdog timer is initialized and starts counting after a write instruction to

this register. The watchdog timer value is always initialized to "7FFFh" regardless

of whatever value is written.

Watchdog Timer Start Register

(1)

Symbol Address After Reset

WDTS 000Eh Indeterminate

Function

RW

b7 b0

WO

NOTE

1. Write to the WDTS register after the watchdog timer interrupt request is generated.

Watchdog timer count (32768)

on-chip oscillator clock

Watchdog timer period =