Rev.1.02 Jul 01, 2005 page 63 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 9. Interrupt

Under development

This document is under development and its contents are subject to change.

9.5.1 I Flag

The I flag enables or disables the maskable interrupt. Setting the I flag to “1” (enabled) enables the

maskable interrupt. Setting the I flag to “0” (disabled) disables all maskable interrupts.

9.5.2 IR Bit

The IR bit is set to “1” (interrupt requested) when an interrupt request is generated. Then, when the

interrupt request is accepted and the CPU branches to the corresponding interrupt vector, the IR bit is set

to “0” (interrupt not requested).

The IR bit can be set to “0” in a program. Note that do not write “1” to this bit.

9.5.3 ILVL2 to ILVL0 Bits and IPL

Interrupt priority levels can be set using the ILVL2 to ILVL0 bits.

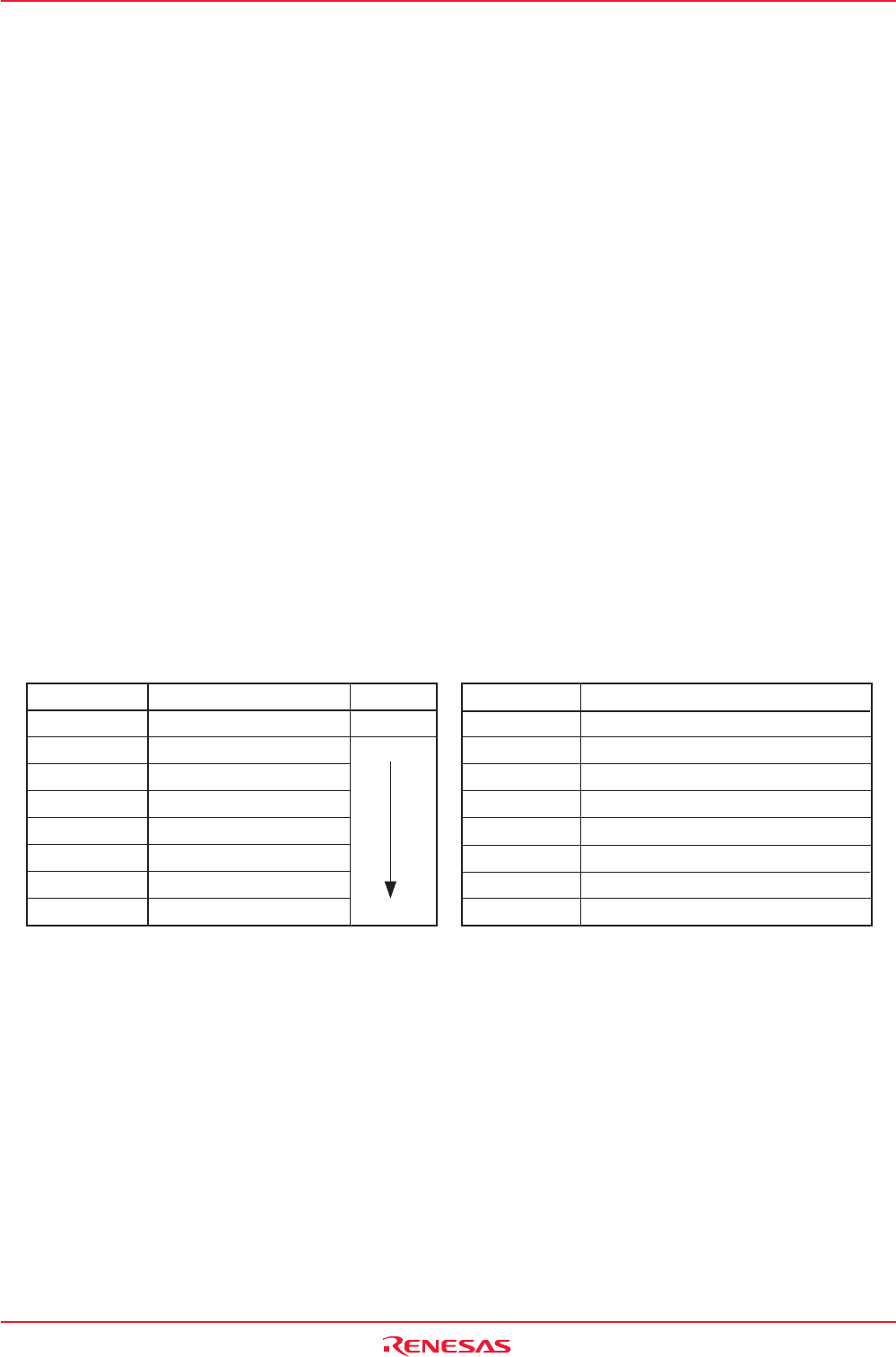

Table 9.3 shows the settings of interrupt priority levels and Table 9.4 shows the interrupt priority levels

enabled by the IPL.

The following are conditions under which an interrupt is accepted:

· I flag = 1

· IR bit = 1

· interrupt priority level > IPL

The I flag, IR bit, ILVL2 to ILVL0 bits and IPL are independent of each other. In no case do they affect one

another.

Table 9.4 Interrupt Priority Levels Enabled by IPL

Table 9.3 Settings of Interrupt Priority Levels

IPL Enabled Interrupt Priority Levels

000b

Interrupt levels 1 and above are enabled

001b

Interrupt levels 2 and above are enabled

010b

Interrupt levels 3 and above are enabled

011b

Interrupt levels 5 and above are enabled

100b

Interrupt levels 5 and above are enabled

101b

Interrupt levels 6 and above are enabled

110b

Interrupt levels 7 and above are enabled

111b

All maskable interrupts are disabled

ILVL2 to ILVL0 Bits

Interrupt Priority Level

Priority Order

000b Level 0

(Interrupt disabled)

-

001b Level 1 Low

010b Level 2

011b Level 3

100b Level 4

101b Level 5

110b Level 6

111b Level 7 High