Rev.1.02 Jul 01, 2005 page 247 of 314

REJ09B0126-0102

M16C/6N Group (M16C/6NL, M16C/6NN) 20. Flash Memory Version

Under development

This document is under development and its contents are subject to change.

20.3.5 Software Commands

Software commands are described below. The command code and data must be read and written in 16-bit

unit, to and from even addresses in the user ROM area. When writing command code, the high-order 8

bits (D15 to D8) are ignored.

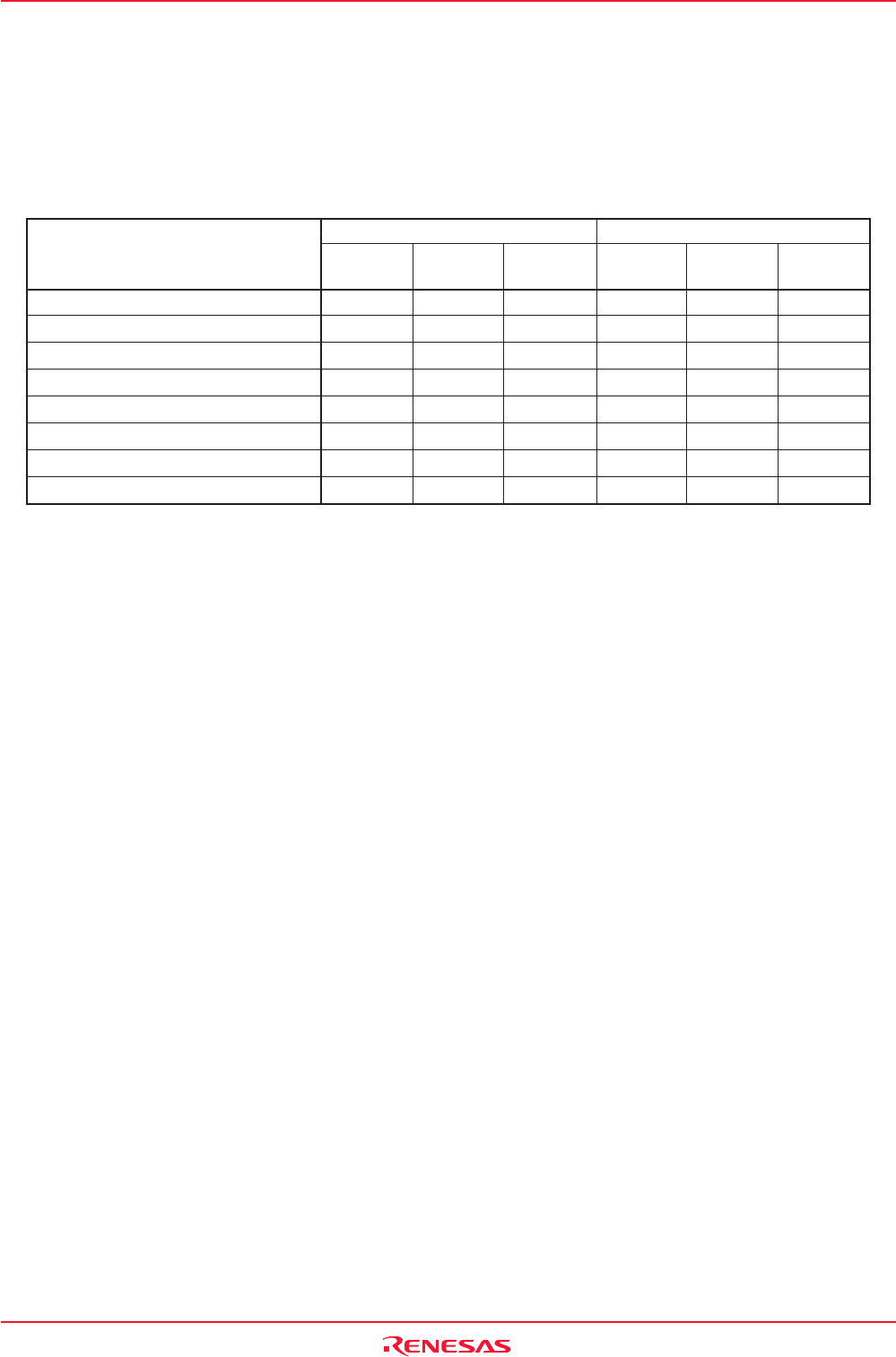

Table 20.4 lists the software commands.

Table 20.4 Software Commands

Read Array

Read Status Register

Clear Status Register

Program

Block Erase

Erase All Unlocked Block

(1)

Lock Bit Program

Read Lock Bit Status

Write

Write

Write

Write

Write

Write

Write

Write

✕

✕

✕

WA

✕

✕

BA

✕

xxFFh

xx70h

xx50h

xx40h

xx20h

xxA7h

xx77h

xx71h

-

Read

-

Write

Write

Write

Write

Write

-

SRD

-

WD

xxD0h

xxD0h

xxD0h

xxD0h

-

✕

-

WA

BA

✕

BA

BA

Mode Address

Data

(D15 to D0)

Mode Address

First Bus Cycle

Second Bus Cycle

Software Command

Data

(D15 to D0)

SRD:data in SRD register (D7 to D0)

WA: Address to be written (The address specified in the first bus cycle is the same even address as the

address specified in the second bus cycle.)

WD: 16-bit write data

BA: Highest-order block address (must be an even address)

✕: Any even address in the user ROM area

xx: High-order 8 bits of command code (ignored)

NOTE

1. It is only blocks 0 to 12 that can be erased by the erase all unlocked block command.

Block A cannot be erased. The block erase command must be used to erase the block A.

20.3.5.1 Read Array Command (FFh)

The read array command reads the flash memory.

By writing command code “xxFFh” in the first bus cycle, read array mode is entered. Content of a

specified address can be read in 16-bit unit after the next bus cycle.

The microcomputer remains in read array mode until another command is written. Therefore, contents

from multiple addresses can be read consecutively.

20.3.5.2 Read Status Register Command (70h)

The read status register command reads the status register (refer to 20.3.7 Status Register (SRD

Register) for detail).

By writing command code “xx70h” in the first bus cycle, the status register can be read in the second bus

cycle. Read an even address in the user ROM area.

Do not execute this command in EW1 mode.

20.3.5.3 Clear Status Register Command (50h)

The clear status register command clears the status register.

By writing “xx50h” in the first bus cycle, the FMR07, FMR06 bits in the FMR0 register are set to “00b”

and the SR5, SR4 bits in the status register are set to “00b”.