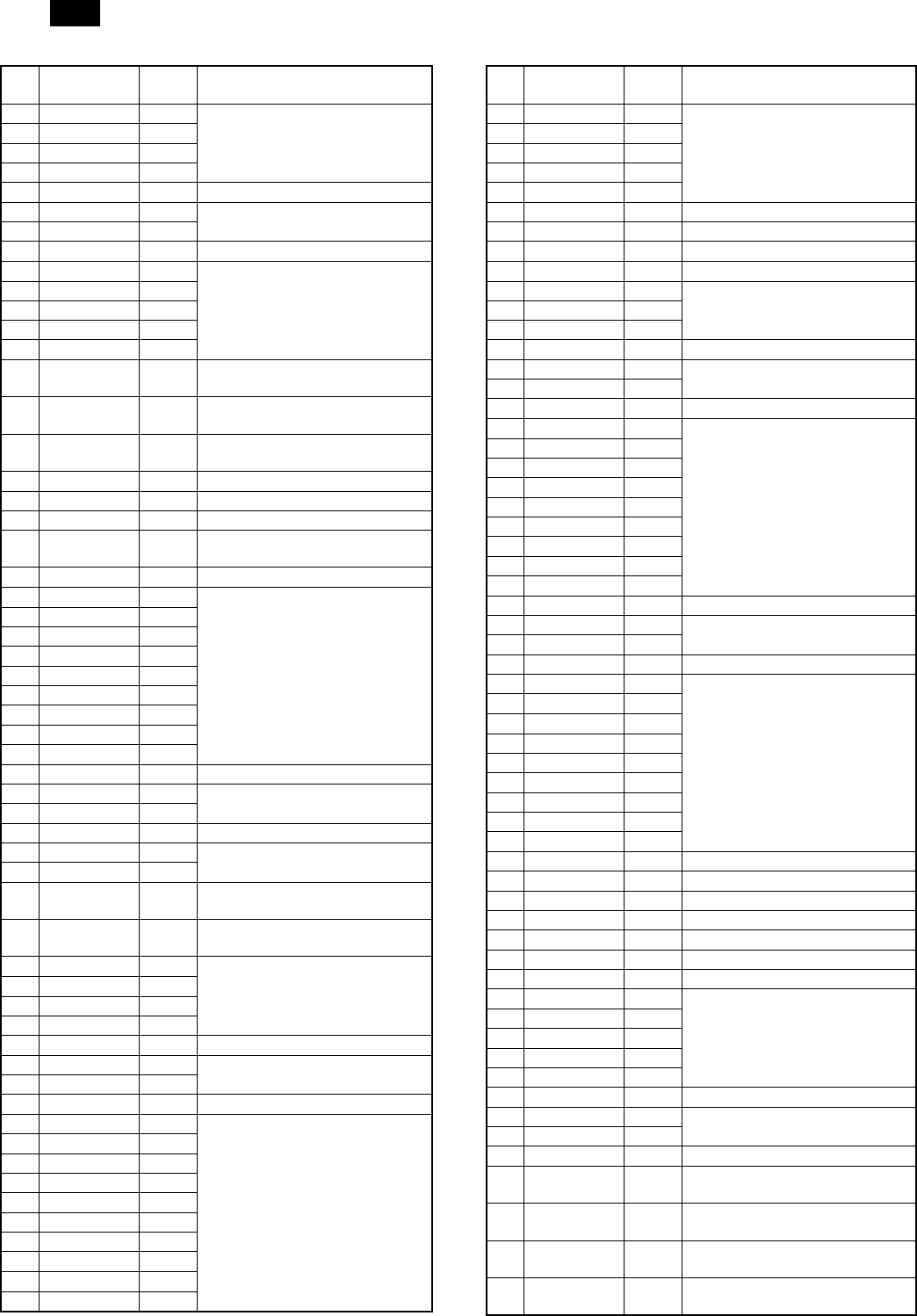

PIN

No.

Signal name IN/OUT Description

27 MDATA10 IN/OUT

Data bus of DRAM (page memory)

28 MDATA9 IN/OUT

29 MDATA8 IN/OUT

30 MDATA7 IN/OUT

31 3.3V Power

32 MDATA6 IN/OUT

Data bus of DRAM (page memory)

33 MDATA5 IN/OUT

34 GND Power

35 MDATA4 IN/OUT

Data bus of DRAM (page memory)

36 MDATA3 IN/OUT

37 MDATA2 IN/OUT

38 MDATA1 IN/OUT

39 MDATA0 IN/OUT

40 /RAS0 OUT RAS signal 0 of DRAM (page

memory)

41 /RAS1 OUT RAS signal 1 of DRAM (page

memory)

42 /RAS2 OUT RAS signal 2 of DRAM (page

memory)

43 /RAS64 OUT (Not used)

44 3.3V Power

45 /RAS16 OUT (Not used)

46 MAD0 OUT Address bus of DRAM (page

memory)

47 GND Power

48 MAD1 OUT

Address bus of DRAM (page

memory)

49 MAD2 OUT

50 MAD3 OUT

51 MAD4 OUT

52 MAD5 OUT

53 MAD6 OUT

54 MAD7 OUT

55 MAD8 OUT

56 MAD9 OUT

57 3.3V Power

58 MAD10 OUT Address bus of DRAM (page

memory)

59 MAD11 OUT

60 GND Power

61 /CAS0 OUT CAS signal of DRAM (page

memory)

62 /CAS1 OUT

63 /OE OUT Read enable signal of DRAM

(page memory)

64 /WE OUT Write enable signal of DRAM (page

memory)

65 OUTD0 OUT

(Not used)

66 OUTD1 OUT

67 OUTD2 OUT

68 OUTD3 OUT

69 3.3V Power

70 OUTD4 OUT

(Not used)

71 OUTD5 OUT

72 GND Power

73 OUTD6 OUT

(Not used)

74 OUTD7 OUT

75 OUTD8 OUT

76 OUTD9 OUT

77 OUTD11 OUT

78 OUTD10 OUT

79 OUTD12 OUT

80 OUTD13 OUT

81 OUTD14 OUT

82 OUTD15 OUT

PIN

No.

Signal name IN/OUT Description

83 /HSYNC OUT

(Not used)

84 /PCLPRD IN

85 /PCLREQ OUT

86 /PCLACK IN

87 /PCLCS IN

88 3.3V Power

89 GND Power

90 5V Power

91 GND Power

92 /FAXPRD IN

(Not used)

93 /FAXREQ OUT

94 /FAXACK IN

95 3.3V Power

96 /FAXCS IN

(Not used)

97 /ESPRD IN

98 GND Power

99 /ESREQ OUT

(Not used)

100 /ESACK IN

101 /ESCS IN

102 PARAD0 IN/OUT

103 PARAD1 IN/OUT

104 PARAD2 IN/OUT

105 PARAD3 IN/OUT

106 PARAD4 IN/OUT

107 PARAD5 IN/OUT

108 5V Power

109 PARAD6 IN/OUT

(Not used)

110 PARAD7 IN/OUT

111 GND Power

112 /REV OUT

(Not used)

113 INIT IN

114 /SLCTIN IN

115 /AUTOFD IN

116 /STB IN

117 /ACK OUT

118 BUSY OUT

119 PE OUT

120 /FAULT OUT

121 5V Power

122 SLCT OUT (Not used)

123 /TESTPIN0 IN High: Normal Low: Test

124 GND Power

125 PFCLK IN Write clock

126 /TESTPIN1 IN High: Normal Low: Test

127 /SYNCEN OUT Jitter adjustment IC trigger signal

128 SD10 IN/OUT

Data line to SRAM before are

separation

129 SD11 IN/OUT

130 SD12 IN/OUT

131 SD13 IN/OUT

132 SD14 IN/OUT

133 5V Power

134 SD15 IN/OUT

Data line to SRAM before are

separation

135 SD16 IN/OUT

136 GND Power

137 SD17 IN/OUT Data line to SRAM before are

separation

138 SOE1 OUT Read enable line to SRAM before

area separation

139 SWE1 OUT Write enable line to SRAM before

area separation

140 SCS1 OUT Chip select line to SRAM before

area separation

AR-161

AR-160/161 FM/E [13] ELECTRICAL SECTION 12/1/1998

13 – 6