SSI

EPS2U Power Supply Design Guide, V2.1

6.8 Ripple / Noise

STATUS

Required

The maximum allowed ripple/noise output of the power supply is defined in Table 22. This is measured over a

bandwidth of 0 Hz to 20 MHz at the power supply output connectors. A 10 µF tantalum capacitor in parallel with a

0.1 µF ceramic capacitor are placed at the point of measurement.

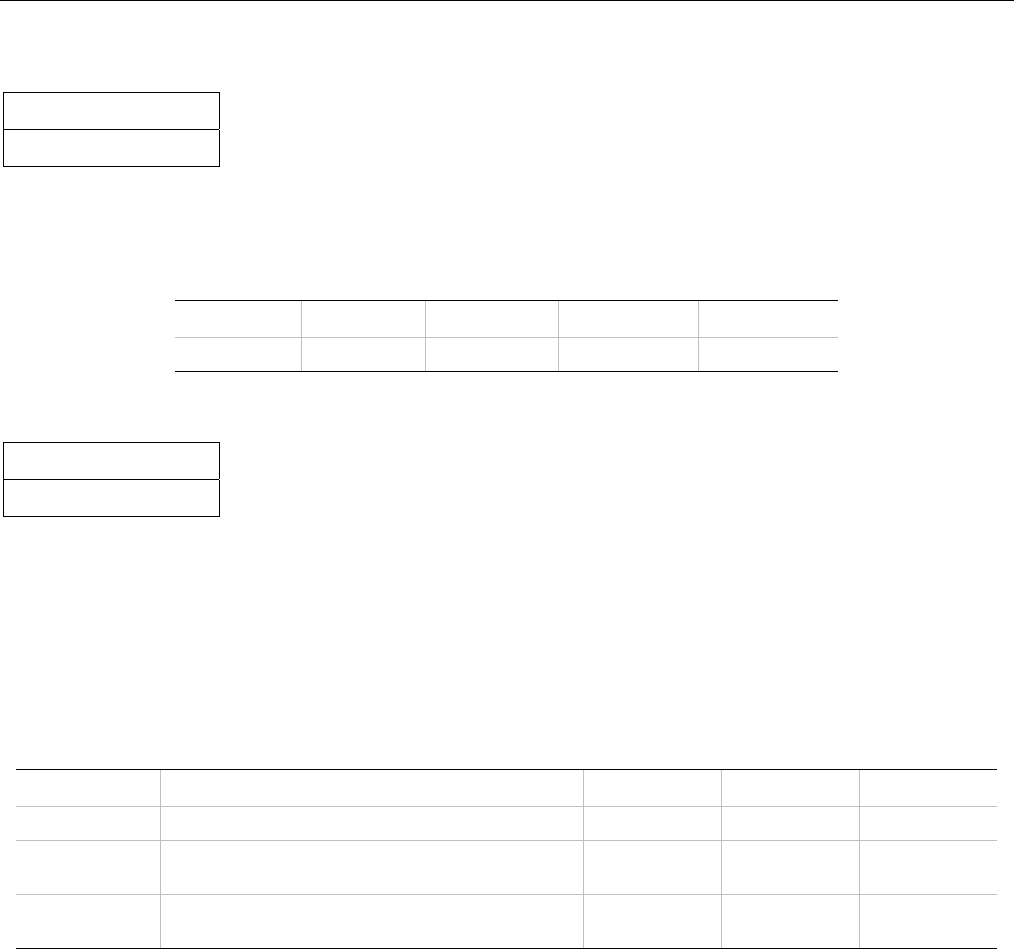

Table 22: Ripple and Noise

+3.3 V +5 V +12 V -12 V +5 VSB

50 mVp-p 50 mVp-p 120 mVp-p 120 mVp-p 50 mVp-p

6.9 Timing Requirements

STATUS

Required

These are the timing requirements for the power supply operation. The output voltages must rise from 10% to

within regulation limits (T

vout_rise

) within 5 to 70 ms. The +3.3 V, +5 V and +12 V output voltages should start to

rise at about the same time. All outputs must rise monotonically. The +5 V output needs to be greater than the

+3.3 V output during any point of the voltage rise. The +5V output must never be greater than the +3.3V output

by more than 2.25 V. Each output voltage shall reach regulation within 50 ms (T

vout_on

) of each other during turn

on of the power supply. Each output voltage shall fall out of regulation within 400 ms (T

vout_off

) of each other

during turn off. Figure 2 and Figure 3 show the turn ON and turn OFF timing requirements. In Figure 3, the

timing is shown with both AC and PSON# controlling the ON/OFF of the power supply.

Table 23: Output Voltage Timing

Item Description MIN MAX Units

T

vout_rise

Output voltage rise time from each main output. 5 70 ms

T

vout_on

All main outputs must be within regulation of each

other within this time.

50 ms

T

vout_off

All main outputs must leave regulation within this

time.

400 ms

- 21 -