SSI

EPS2U Power Supply Design Guide, V2.1

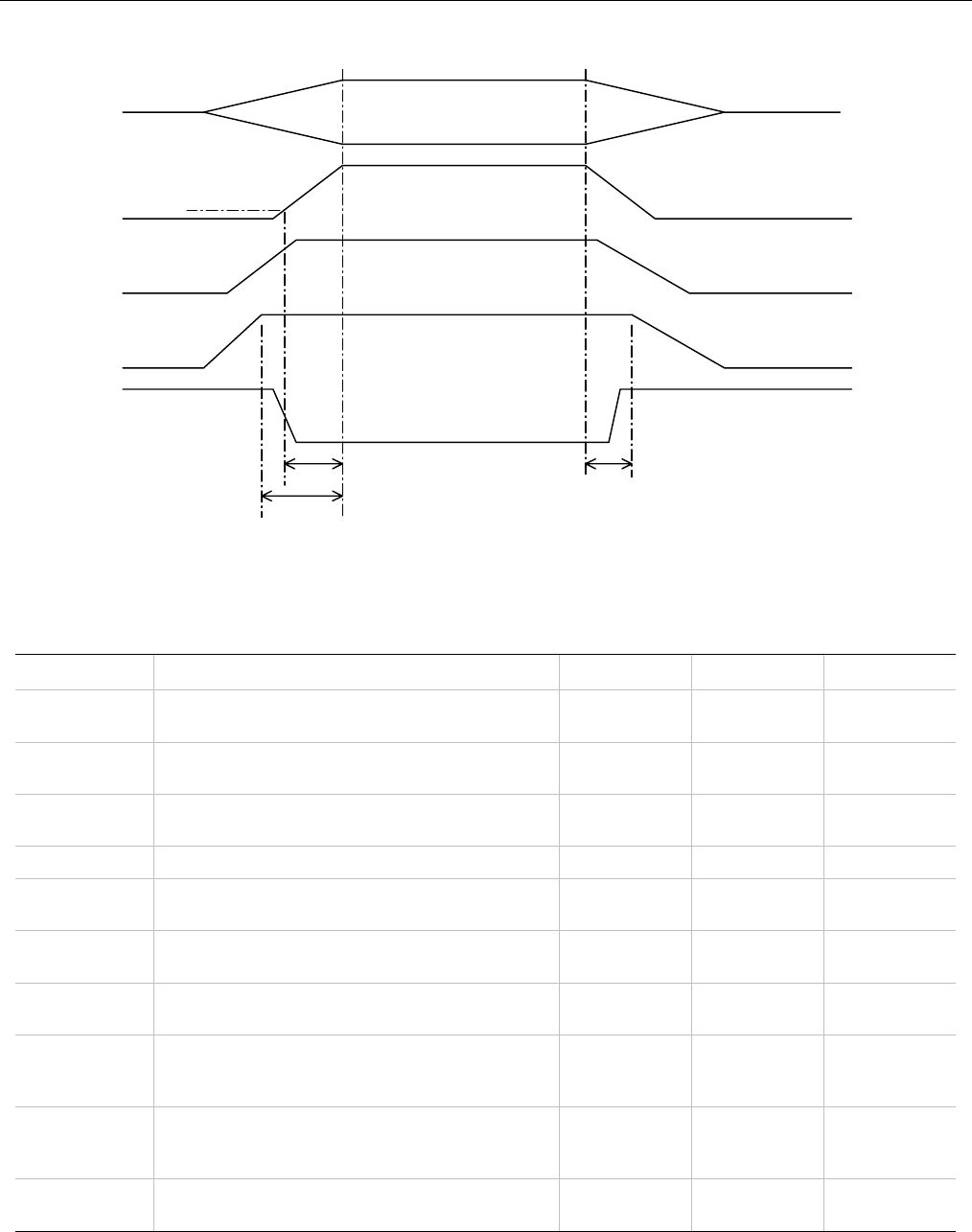

V4

V3

V2

V1

T

vout_off

T

vout_on

T

vout

_

rise

10% Vout

Vout

Figure 2: Output Voltage Timing

Table 24: Turn On/Off Timing

Item Description MIN MAX UNITS

T

sb_on_delay

Delay from AC being applied to 5 VSB being

within regulation.

1500 ms

T

ac_on_delay

Delay from AC being applied to all output voltages

being within regulation.

2500 ms

T

vout_holdup

Time all output voltages stay within regulation

after loss of AC.

18 ms

T

pwok_holdup

Delay from loss of AC to deassertion of PWOK. 17 ms

T

pson_on_delay

Delay from PSON

#

active to output voltages within

regulation limits.

5 400 ms

T

pson_pwok

Delay from PSON

#

deactive to PWOK being

deasserted.

50 ms

T

pwok_on

Delay from output voltages within regulation limits

to PWOK asserted at turn on.

100 1000 ms

T

pwok_off

Delay from PWOK deasserted to output voltages

(3.3 V, 5 V, 12 V, -12 V) dropping out of regulation

limits.

1 ms

T

pwok_low

Duration of PWOK being in the deasserted state

during an off/on cycle using AC or the PSON#

signal.

100 ms

T

sb_vout

Delay from 5 VSB being in regulation to O/Ps

being in regulation at AC turn on.

50 1000 ms

- 22 -